## Laboratory practical with the C8051Fxxx microcontroller family

Gingl Zoltán, Mingesz Róbert

#### 2014

A tananyag a TÁMOP-4.1.2.A/1-11/1-2011-0104 "A felsőfokú informatikai oktatás minőségének fejlesztése, modernizációja" c. projekt keretében a Pannon Egyetem és a Szegedi Tudományegyetem együttműködésében készült.

# Laboratory practicals with the C8051Fxxx microcontroller family

#### **Authors:**

Zoltán Gingl and Róbert Zoltán Mingesz

#### **Keywords:**

Microcontrollers, embedded programming, timers, counters, serial communication, analogue-to-digital conversion, sensors.

#### **Summary**

The purpose of this book is to help the teaching of the applications of microcontrollers in various projects. Several books and manuals are available [1-19]; this book contributes to these by covering the knowledge needed to use the powerful C8051Fxxx family of microcontrollers from Silicon Laboratories in practice. Our aim was to synthesise the most useful information found in manuals, tutorials, datasheets, user forums, application notes, electronic design notes and example code in a single book. Most chapters feature brief application guidelines and troubleshooting based on our teaching and development experience. This can be highly useful for students and for developers as well.

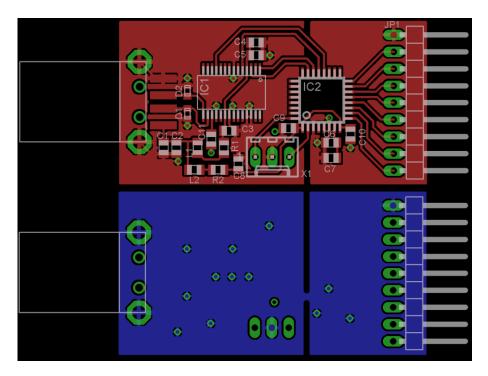

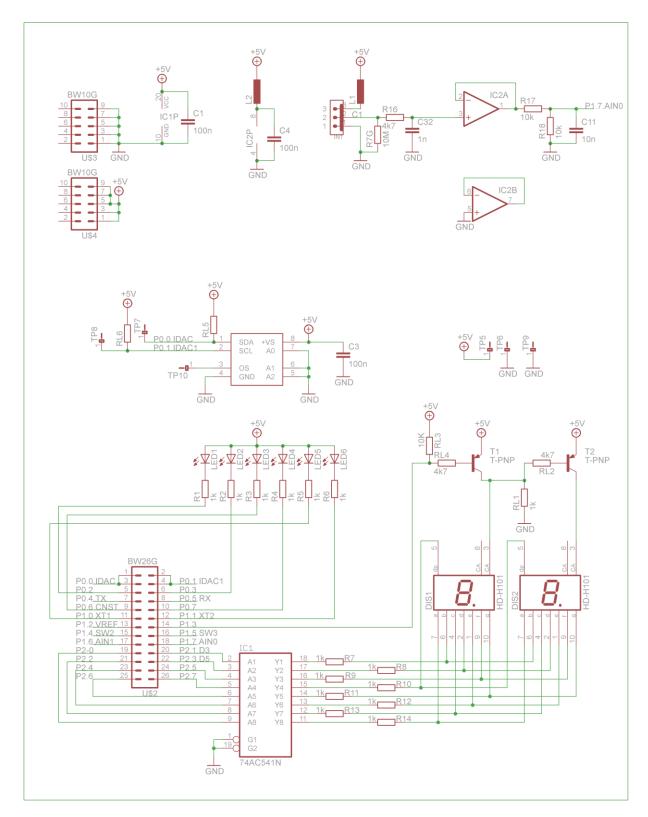

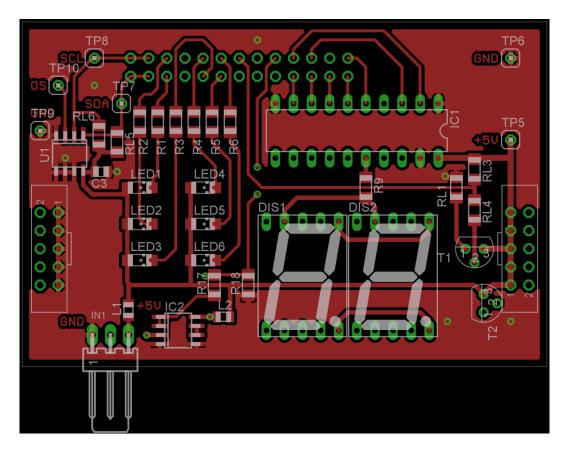

We believe that the brief discussion of the architecture, peripherals, analogue and digital signal interfacing helps to understand how these can be used to build various applications. We provide tested example code and recommended exercises and discuss several application examples, including single-supply analogue signal conditioning, sensor interfacing and microcontroller-host computer communication. In the last chapter, we show the schematic and layout of an extension board that supports the use of the C8051F410DK development kit and can also be modified for use with other target boards.

Up-to-date, high quality references were chosen that are provided by industry leading companies [1–19]. Almost all of the references are available on-line on the companies' web pages.

#### TABLE OF CONTENTS

| 1 | Int | roduction                                                            | 6       |

|---|-----|----------------------------------------------------------------------|---------|

|   | 1.1 | Real-world signal processing and control                             | 6       |

|   | 1.2 | Microcontrollers                                                     | 7       |

|   | 1.3 | Microcontroller core and integrated peripherals                      | 8       |

|   | 1.4 | Microcontroller classification                                       | 13      |

| 2 | Arc | hitecture and properties of the C8051Fxxx microcontroller family     | 14      |

|   | 2.1 | 8051 microcontrollers                                                | 14      |

|   | 2.2 | The C8051Fxxx microcontroller family                                 | 14      |

|   | 2.3 | The CIP-51 architecture                                              | 15      |

| 3 | Ass | embler and C programming                                             | 28      |

|   | 3.1 | SDCC C compiler                                                      | 28      |

|   | 3.2 | Interrupt programming in assembler                                   | 30      |

|   | 3.3 | Interrupt handling in C                                              | 31      |

|   | 3.4 | Interrupt programming guidelines                                     | 33      |

|   | 3.5 | Using an integrated development environment and the associated tools | 34      |

|   | 3.6 | Config Wizard                                                        | 35      |

| 4 | Dig | ital input and output; crossbar                                      | 37      |

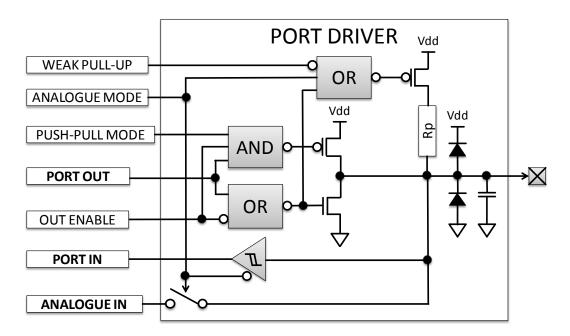

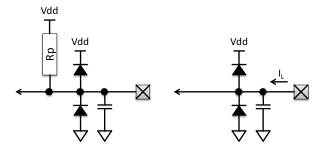

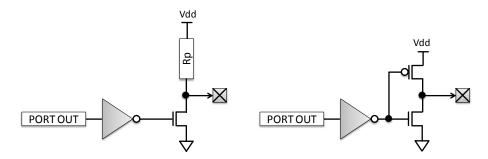

|   | 4.1 | The I/O structure                                                    | 37      |

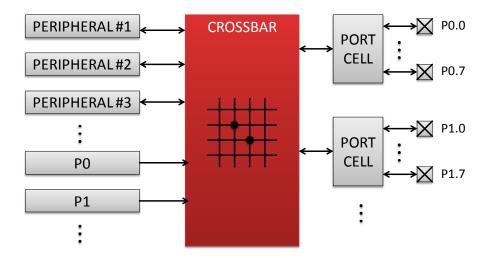

|   | 4.2 | Crossbar                                                             | 39      |

|   | 4.3 | Port I/O applications                                                | 40      |

|   | 4.4 | Application guidelines                                               | 48      |

|   | 4.5 | Troubleshooting                                                      | 49      |

|   | 4.6 | Exercises                                                            | 49      |

| 5 | Tin | ners and counters                                                    | 51      |

|   | 5.1 | Timer o and Timer 1                                                  | 51      |

|   | 5.2 | Timer 2, Timer 3 and Timer 4                                         | ···· 53 |

|   | 5.3 | Timer applications                                                   | 55      |

|   | 5.4 | Application guidelines                                               | 59      |

|   | 5.5 | Troubleshooting                                                      | 60      |

|   | 5.6 | Exercises                                                            | 61      |

| 6 | Pro | grammable counter array                                              | 62      |

|   | 6.1 | Edge-triggered capture mode                                          | 62      |

| 6.2   | Software timer and high-speed output mode | 63  |

|-------|-------------------------------------------|-----|

| 6.3   | Frequency output mode                     | 64  |

| 6.4   | 8-bit and 16-bit PWM modes                | 65  |

| 6.5   | Application guidelines                    | 67  |

| 6.6   | Troubleshooting                           | 68  |

| 6.7   | Exercises                                 | 68  |

| 7 Se  | erial communication peripherals           | 70  |

| 7.1   | UART                                      | 70  |

| 7.2   | SPI                                       | 75  |

| 7.3   | SMBus                                     | 79  |

| 7.4   | C standard I/O redirection                | 83  |

| 7.5   | Exercises                                 | 84  |

| 8 Ar  | nalogue peripherals                       | 85  |

| 8.1   | Comparators                               | 85  |

| 8.2   | Voltage reference                         | 88  |

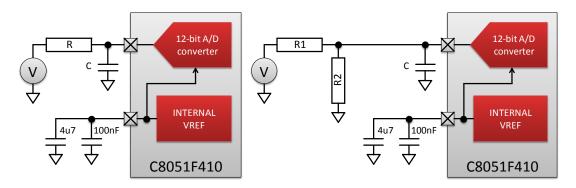

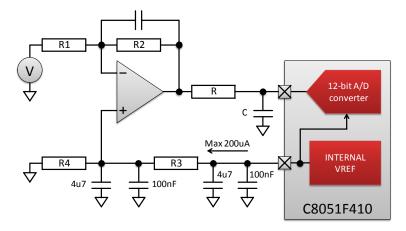

| 8.3   | ADC                                       | 90  |

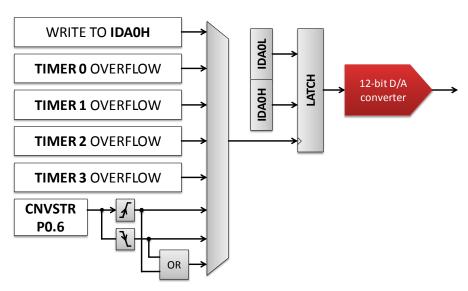

| 8.4   | DAC                                       | 97  |

| 8.5   | Temperature sensor                        | 99  |

| 8.6   | Exercises                                 | 99  |

| 9 Se  | ensor interfacing                         | 101 |

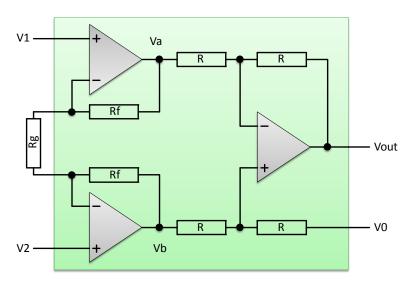

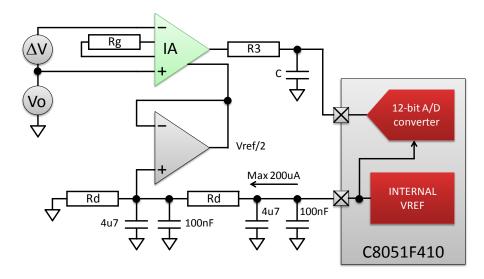

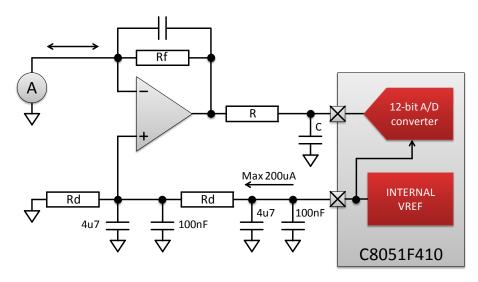

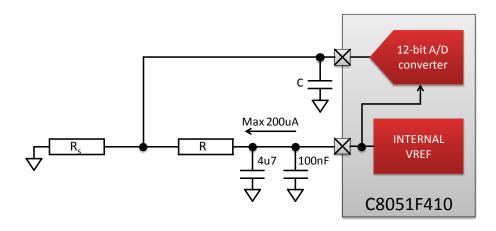

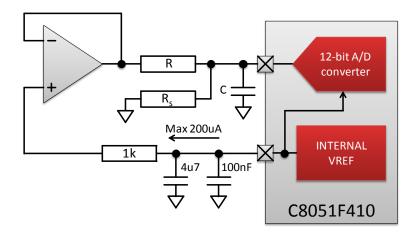

| 9.1   | Voltage output sensors                    | 101 |

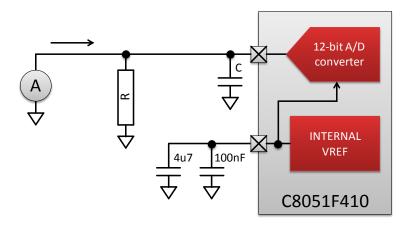

| 9.2   | Current output sensors                    | 103 |

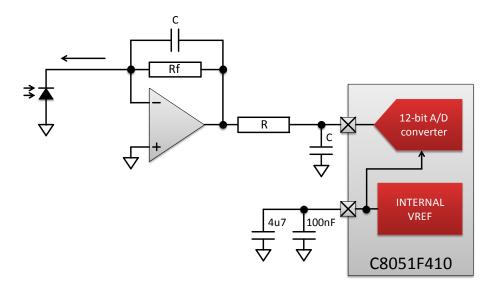

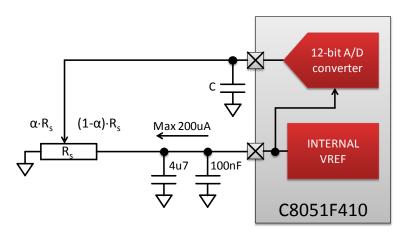

| 9.3   | Resistive sensors                         | 104 |

| 9.4   | Exercises                                 | 106 |

| 10 Re | eal-time clock                            | 108 |

| 10.2  | Exercises                                 | 110 |

| 11 W  | atchdog and power supply monitor          | 111 |

| 11.1  | The watchdog timer                        | 111 |

| 11.2  | Supply monitor                            | 111 |

| 11.3  | Exercises                                 | 112 |

| 12 Lo | ow-power and micropower applications      | 113 |

| 12.1  | Low-power modes                           | 113 |

| 12.2  | Clock speed tuning                        | 113 |

| 12.3  | Peripheral power consumption              | 114 |

| 12.4 | Supply voltage                        | .114  |  |  |  |  |  |

|------|---------------------------------------|-------|--|--|--|--|--|

| 12.5 | Exercises                             | . 116 |  |  |  |  |  |

| 13 U | SB, wired and wireless communications | . 117 |  |  |  |  |  |

| 13.1 | USB-UART interfaces                   | . 117 |  |  |  |  |  |

| 13.2 | Wireless communication possibilities  | .119  |  |  |  |  |  |

| 13.3 | Exercises                             | 120   |  |  |  |  |  |

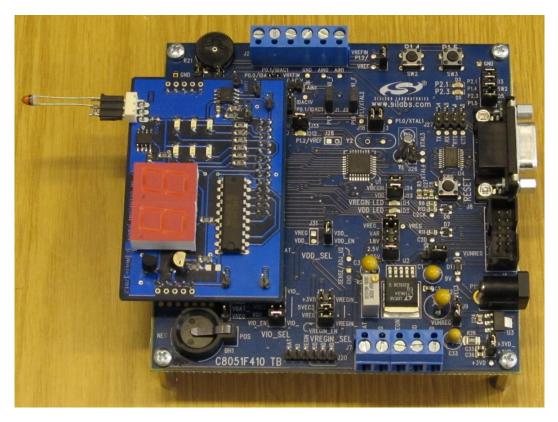

| 14 D | evelopment kit                        | .121  |  |  |  |  |  |

| 14.1 | The C8051F410 development kit         | .121  |  |  |  |  |  |

| 14.2 | Extension board                       | .121  |  |  |  |  |  |

| 15 A | cknowledgements                       | .125  |  |  |  |  |  |

| 16 R | References126                         |       |  |  |  |  |  |

#### 1 Introduction

#### 1.1 Real-world signal processing and control

It is a typical aim to construct machines to make life more comfortable and more economical. From simple mechanical machines to advanced electronic devices such as smart phones the range is really wide. The most efficient devices are based on electronics, sophisticated signal processing and modern software.

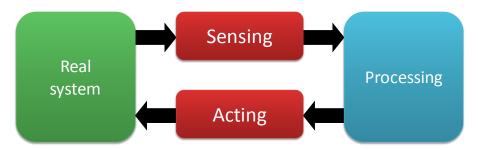

In order to allow processing, real signals must be converted into another format that can be processed and the result should be used for intervention, as shown in Figure 1.1.

Figure 1.1. General real-world interaction.

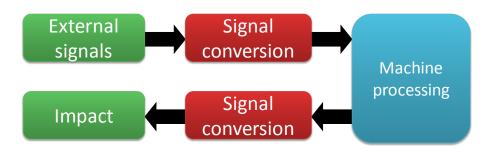

The same principle is used in machines in general (Figure 1.2).

Figure 1.2. Machine – real world interaction.

The most efficient devices use analogue and digital electronics and run software to process information. Many of today's devices are small, battery-operated and incredibly efficient. Again, a good example is the smart phone that integrates telephony, camera, wireless communication, computer, sensors, GPS and many more in a handful of electronics.

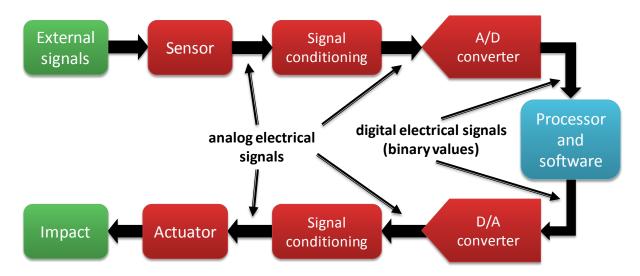

The detailed block diagram of such an electronic device is shown in Figure 1.3. Sensors convert several physical signals (displacement, force, pressure, acceleration, temperature, light intensity, etc.) to signals that can be handled by electronics (voltage, current, resistance, capacitance, inductance). The output of sensors is converted to voltage in the proper range (a few volts) that can be easily used in processing. The analogue-to-digital converter translates this voltage to integer numbers for digital processing. A similar principle is applied in the reverse transformations.

Figure 1.3. Electronic device – real world interaction.

Several analogue and digital integrated circuits have been developed to support the manufacture of electronic devices. One of the most compact and most efficient components is the microcontroller.

#### 1.2 Microcontrollers

The microcontroller unit (MCU) is a small but powerful digital building block, a single-chip microcomputer. It contains everything required for operation; very few external components are needed – sometimes only supply decoupling capacitors. Of course, the device must be powered, typically from a single supply voltage that ranges from 1.8 V to 5 V. Sometimes even a coin cell battery suffices.

The microcontroller has several peripherals to sense real-world signals and initiate real-world events, and has a processor core to run software. It is a very flexible, powerful and compact electronic component. Since most of the processing is done by the software, the same hardware can be used for several applications; the performance can be upgraded easily by replacing the software only.

There is a very wide range of microcontrollers on the market from sizes of 2 mm  $\times$  2 mm and from a power consumption of 30  $\mu$ W to a speed of several hundred MHz.

Most modern microcontrollers incorporate comparators, analogue-to-digital and digital-to-analogue converters and temperature sensors – therefore, they are often called mixed-signal (both analogue and digital) microcontrollers.

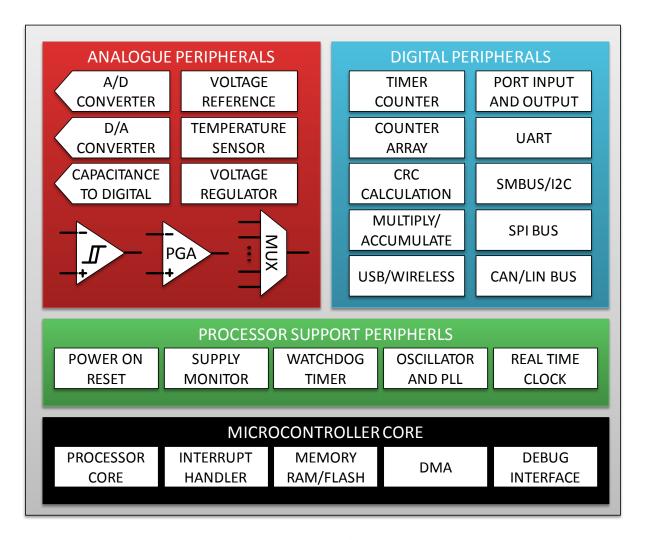

Figure 1.4 illustrates some typical components of a modern mixed-signal microcontroller; the details will be given in the next chapter.

Figure 1.4. Microcontroller components.

#### 1.3 Microcontroller core and integrated peripherals

The microcontroller core is based on a processor with its typical components including an arithmetic logic unit (ALU) and several registers. The architecture may follow the CISC (like the 8051 family) or, more probably, the RISC principles (for example, the PIC, AVR and ARM microcontrollers) in today's popular microcontrollers.

Most of the devices use separate memory for the data and for the program; that is, they have Harvard architecture. This fits well the need for non-volatile program memory and at the same time it prevents code corruption and provides even faster execution in some cases. The word length of the two kinds of memory can also be different. Microcontrollers may use Neumann or Harvard architecture, or the user can even configure the memory usage (for example, in the case of the ARM Cortex-M3 32-bit microcontroller family).

All modern microcontrollers have volatile (SRAM) memory and non-volatile, reprogrammable flash memory. The flash memory contains the code, so no external integrated circuits are needed. The flash memory can be reprogrammed by special programming devices using a few (from 2 to 6-8) pins of the microcontroller (in-circuit programming, JTAG) or can even be overwritten by the microcontroller itself in some cases. Additional separate flash or EEPROM may also be integrated to support non-volatile data storage (configuration data, calibration data, statistical data, etc.). The flash memory can be

rewritten about 100000 times, and the typical data retention time is longer than 20 years. The flash memory can be protected, i.e., the code can be prevented from being read by the user.

If the on-chip memory is not enough for a certain application, the developer can choose microcontrollers with an external memory interface that support the connection of static RAM or other memories of various sizes. Note also that this interface may support the use of 'memory mapped' peripherals including A/D converters, D/A converters, FIFO memories, etc.

#### 1.3.1 Processor support

In the following the most typical processor support peripherals will be described briefly.

**Power on reset (POR)** generator. After switching the power on, the supply voltage may rise a bit slowly due to the fact that the supply decoupling and filtering capacitors must be charged and the supply current is limited. At the same time, the digital circuitry needs a certain minimum supply voltage for proper operation, so the start-up of the microcontroller must be delayed until the supply voltage reaches the safe operating level. Having detected the crossing of this level, the POR generates an additional short delay (in the range from below 1 ms to about 100 ms) and finally releases the reset line.

**Power supply monitor** (Brown-out detector). In some cases, the supply voltage may go below the safe operating level even during operation (for example, when sudden heavy current loading occurs). This may result in erroneous code execution, therefore the supply monitor circuit will generate a reset in this case. Note that this feature can be disabled by the programmer, although the use of the supply monitor is strongly recommended.

**Low-dropout (LDO) regulator.** Some microcontrollers have separate voltage levels for their core and digital input and output ports. Integrated voltage regulators can provide stable and sometimes even programmable supply voltage from the input supply voltage. Low-dropout regulators need only a slightly (roughly about 100 mV) higher input supply voltage than their output voltage.

Watchdog timer (WDT). Even properly powered processors can fall into infinite loops or get disturbed by electromagnetic or conducted interference (for example, in the case of lightning or power line transients), which may cause serious problems in several applications (motor control, heating control, healthcare devices, etc.). The watchdog timer refresh register needs to be written within a certain amount of time (that can be typically programmed from tens of milliseconds to several seconds); otherwise, a reset will be generated. If the code writes to the register, the timer will be restarted and no reset will be generated. If the processor code execution fails, this will not occur and a reset will be initiated. The best practice is to always use the watchdog timer except in code development phase or in simple test projects. The watchdog timer is enabled automatically upon reset in quality microcontrollers.

**Oscillator, PLL**. All processors need a clock signal to schedule instruction execution. Modern microcontrollers have on-chip oscillators but also support the use of external quartz crystals or external clock signals. Optional phase-locked loop (PLL) clock multipliers often combined with clock dividers allow the generation of a wide range of higher processor clock frequencies. Typically, on-chip oscillators have an accuracy of 1%-20%, while the precision of

crystal oscillators can fall below 0.01%. The developer can choose the solution that suits the particular application best.

**Debug interface.** This interface is used by the integrated development environment to download code to the flash memory. Memory upload is also supported and the developer can program the security bits to protect the code from being uploaded. The debug port allows single stepping, supports breakpoints and can track the content of variables, memory and peripheral registers. The debug interface makes code development and testing easy and it is an essential tool for all modern microcontrollers. The most commonly used interface standard is called JTAG (Joint Test Action Group, IEEE 1149.1 Standard Test Access Port and Boundary-Scan Architecture).

#### 1.3.2 Digital peripherals

Digital peripherals include the digital input/output pin drivers and internal digital circuits related to timing, communication and computation acceleration.

General-purpose input/output (GPIO), port input/output (Port I/O). The processor reads from and writes to memory and all on-chip peripherals using the bidirectional data bus. Some processors may also incorporate a direct memory access (DMA) controller, which transfers data between memory and a peripheral without processor intervention. The data is valid only for a short duration in order to free the bus for other transactions, so the general purpose output requires latches that can keep the data until the code writes new data to it. The output of these latches is connected to the pins of the chip and can drive LEDs and provide logic output signals for external digital circuit inputs. These signals are mostly arranged in 8-bit groups to form a byte. The pins can also be configured as digital inputs that can be read any time by the microcontroller. This way buttons, switches and digital signals can be connected as well with the help of internal or external pull-up resistors.

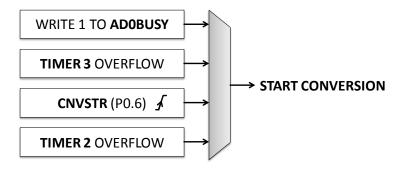

**Timer/Counter modules.** Microcontrollers are designed to control electronic equipment for household, automotive, industrial, test and measurement applications; therefore, timing, event counting, periodic event generation and time duration measurement are important. All microcontrollers contain 8-, 16- or 32-bit counters that can be configured as timers (when an oscillator drives the counter) or as counters, when the rising or the falling edge of an external signal increments the counter. Timers also provide timing for serial communication peripherals, A/D converters and D/A converters.

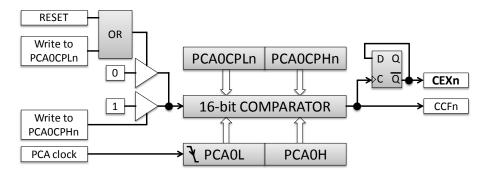

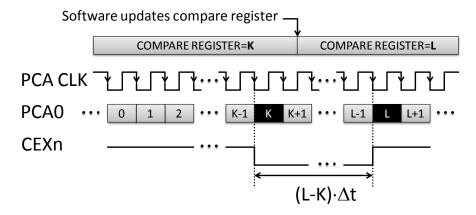

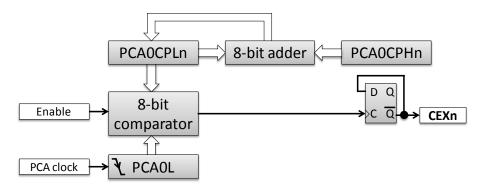

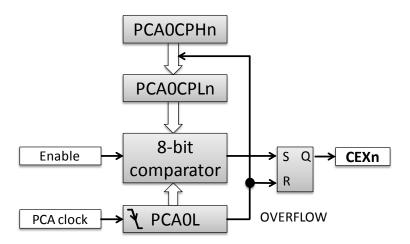

**Programmable Counter Array (PCA).** The PCA contains a simple free-running counter that is driven by an oscillator. There are several (from 3 to 6) independent compare/capture registers that can be used to latch the counter value upon an event (a change in a digital input signal). These registers can also hold data to be compared with the counter value and to generate an event when a match occurs. The PCA can be used to measure pulse width, period or frequency, to generate pulse width modulated (PWM) signals and special logic signal patterns, periodic interrupts and even more.

**Real-Time clock (RTC).** In order to measure the real time or synchronise events to it, a dedicated precise oscillator and an associated 32 to 48-bit counter is provided in some microcontrollers. The oscillator typically uses 32768-Hz tuning fork crystals and a very low power oscillator. Practically, a clock is integrated into the microcontroller that can be powered from a button battery and can run even if the processor is not powered. Besides

measuring real time, this peripheral can serve to wake the microcontroller up at a certain time – in other words, to provide alarm function.

Computing support (MAC, CRC, AES). Some microcontrollers contain computation and digital signal processing acceleration hardware. For example, 8-bit microcontrollers can have a multiply and accumulate (MAC) unit that can multiply and add 16-bit data in a few clock cycles. This can be used efficiently in digital filtering and to compute fast Fourier transforms (FFT). Cyclic redundancy check (CRC) is frequently used to check data integrity in communications and the Advanced Encryption Standard (AES) algorithm is also supported by some microcontrollers.

#### 1.3.3 Communication

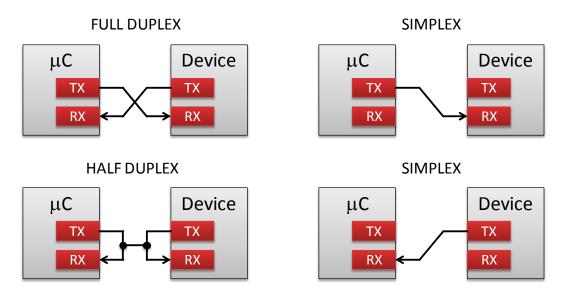

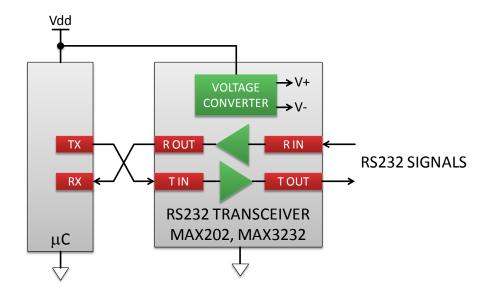

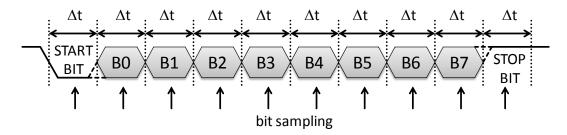

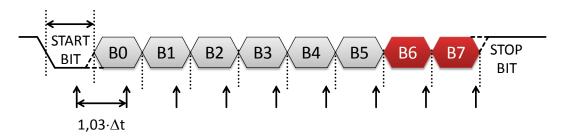

Universal Asynchronous Receiver/Transmitter (UART). This serial (one bit at a time) communication interface uses one wire to send and another wire to receive bits of a byte. The sender and receiver must have a closely matched time base that determines the duration of transmitting a bit, since no timing synchronisation is provided. Every transaction is initiated by sending a start bit, followed by the data bits. The receiver detects the start bit and can then decode the data bits by sampling the signal at evenly spaced time instants. The UART interface is used for low wire count inter-processor communications, host computer communication via USB-UART interfaces, infrared communications and device-to-device communications. In most cases, it is a two-device bus; the use of more devices introduces hardware and software overheads.

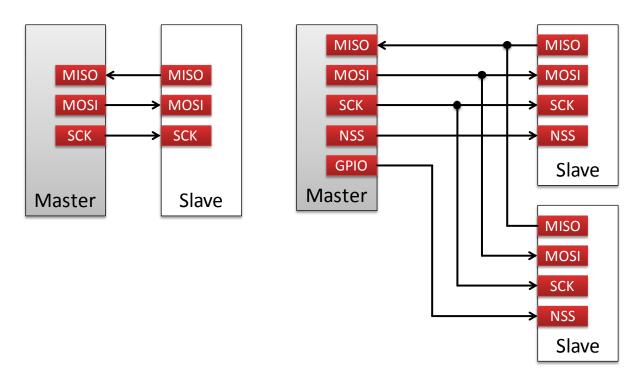

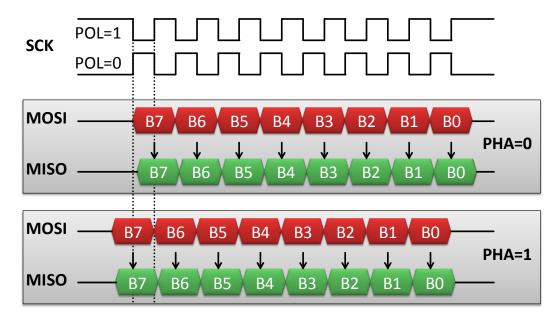

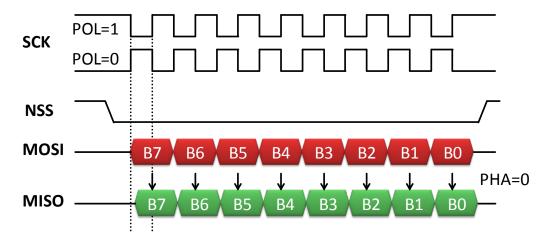

**Serial Peripheral Interface (SPI).** The SPI interface is typically used for high-speed communication with off-chip peripherals including analogue-to-digital converters, digital-to-analogue converters, digital output sensors and other processors. Two wires are used to carry data bits in two directions and one wire for a clock signal that synchronises the timing between the communicating devices. A rising or a falling edge of this signal indicates the beginning of the transmission of each bit. A fourth signal may also be used to provide a frame for the communication. If this signal is inactive, the other signals are ignored, which can be used to connect multiple devices on the same bus and select one for which communication is enabled.

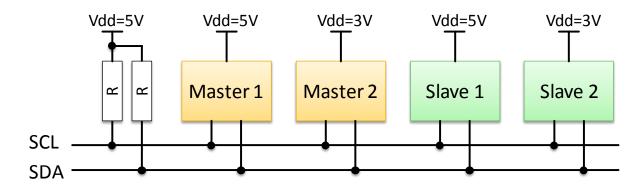

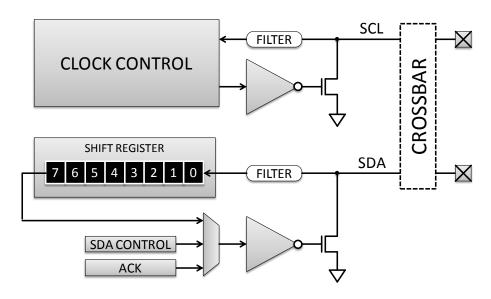

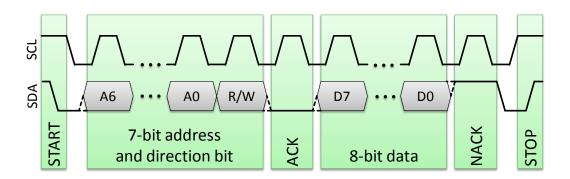

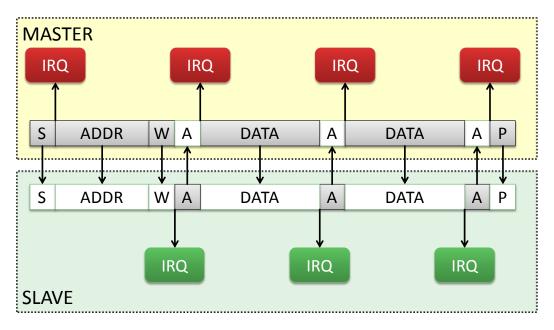

**Inter-Integrated Circuit (IIC or I<sup>2</sup>C) and System Management Bus (SMBus).** This medium-speed interface is specially developed for communication between a host microcontroller and several peripheral chips (memories, data converters, sensors or other processors) on the same printed circuit board or within equipment over only two wires. One wire carries data in both directions, while the other is used to provide a frame (start and stop conditions) for the transaction and to synchronise the transmission of the bits through clock pulses.

Controller Area Network (CAN), Local Interconnect Network (LIN). These serial interfaces are only available on some microcontrollers that target automotive or other industrial applications. Most of the protocol is implemented in hardware.

Universal Serial Bus (USB). The USB is the most popular and innovative interface for connecting peripherals to personal computers or tablets. Some microcontrollers have built-in slave (and rarely host) USB ports. This allows direct connection to the USB port; however, the programmer should know the most important parts of the USB protocol and a driver is typically required on the host computer.

**Wireless communication peripherals.** Wireless communication is becoming a more and more popular interface between small devices, since it supports very flexible location and networking options and no wires are required. There are microcontrollers with integrated wireless transmitters and receivers (transceivers) with several frequency options and a number of wireless protocols can be implemented by software. Bluetooth, ZigBee and the open-source TinyOS system are among the most widely used platforms.

#### 1.3.4 Analogue peripherals

Several microcontrollers have analogue parts to handle analogue signals even without external analogue circuitry. This makes microcontrollers even more compact: a single microcontroller and only a few external components can implement a complete solution for a real-world application that requires the monitoring of signals and the controlling of processes. Microcontrollers that have a significant analogue part and can therefore handle both digital and analogue signals are often called mixed-signal microcontrollers or analogue microcontrollers.

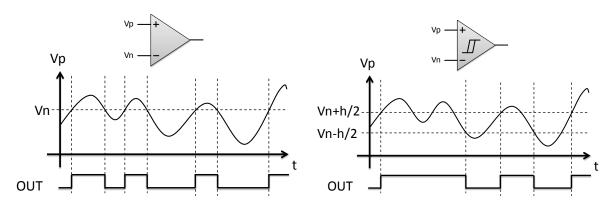

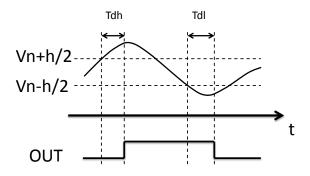

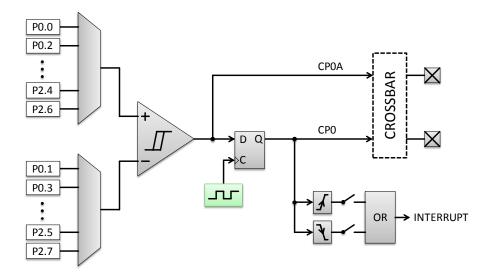

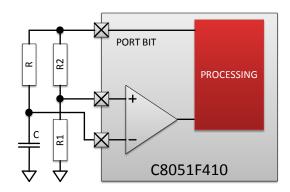

**Comparator.** Comparators have two analogue voltage inputs and a digital output. Their output is logical high if the voltage connected to their positive input is higher than the voltage at their negative input. They may also have hysteresis to reduce potential noise-induced switching.

**Analogue-to-Digital Converter (ADC).** Analogue voltages can be translated into the digital domain using ADCs. The output is an integer number with a various number of bits. A resolution of 10 bits is the most typical, but precision microcontrollers can have 12-, 16- or even 24-bit ADCs. Note that the accuracy is normally less than the resolution; therefore, the datasheet should always be consulted to obtain reliable information.

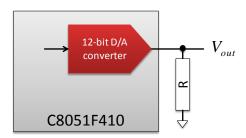

**Digital-to-Analogue Converter (DAC).** DACs output analogue signals proportional to the integer number at their input. The resolution range includes 8, 10, 12 or 16 bits. The output signal can be voltage or current.

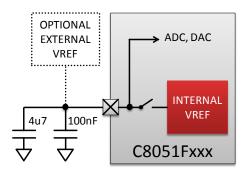

**Voltage reference (VREF).** All data converters (ADCs, DACs) need a reference voltage that serves as an etalon of conversion. The input range of the ADCs and the output range of voltage output DACs are both determined by  $V_{\text{ref}}$ ; in most cases it is between 0 and  $V_{\text{ref}}$ . The internal reference voltage can be switched off to support the use of more precise external reference voltage circuits.

**Capacitance-to-Digital Converter (CDC).** One of the most popular modern user interfaces is based on touch sensing that effectively replaces mechanical buttons, which have limited reliability and lifetime. The change in a capacitance is measured, which change depends on the proximity of the finger of the user from the sensing pad. The capacitance is digitised and the data can be used for evaluation.

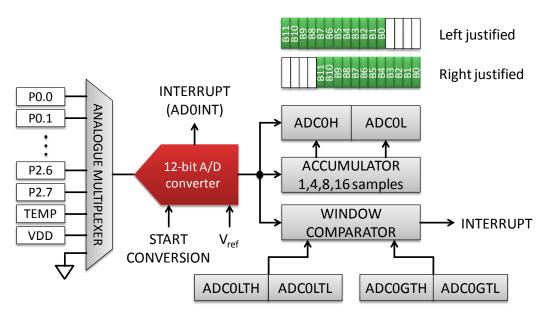

**Analogue Multiplexer (MUX).** Monitoring multiple analogue signals is often needed in real-world applications. This can be supported by a network of switches, called an analogue multiplexer, that connects one of the signals to the input of the ADC at a time. After the conversion of a signal, the next signal can be selected. Since conversion only takes a short time, this means a quasi-simultaneous conversion if the signals change only slowly. However, the different signals are measured at slightly different time instants, which should be considered anyway.

**Programmable Gain Amplifier (PGA).** Some microcontrollers have preamplifiers before their integrated ADCs to support voltage range extension. The preamplifiers can have software-programmable gains of 0.5, 1, 2, 4, 8, 16, 32, 64, 128. Single-ended and differential input PGAs are both available.

**Temperature sensor.** Most mixed-signal microcontrollers include diode-based temperature sensors that can be connected to the input of the internal ADC using the analogue multiplexer. The on-chip sensor outputs a voltage that has linear dependence on the chip temperature. The accuracy of the sensor is roughly about  $\pm 3$  °C. It can be used to protect the device from overheating or to estimate the ambient temperature if the power dissipation of the microcontroller is low enough so that we can neglect self-heating.

#### 1.4 Microcontroller classification

Depending on the different features and according to target applications microcontrollers can be broken down into the following categories:

**General-purpose microcontrollers** have common digital peripherals including timers, GPIO or UART. Their typical clock frequency is around 10 MHz.

**Low power microcontrollers** can operate at lower clock frequencies, from 1 MHz down to tuning fork crystal frequency of 32768 Hz or even below. At 1 MHz the supply current is well below 1 mA, and supply sensitivity is close to 200  $\mu$ A/MHz. During power down state the supply current can fall below 1  $\mu$ A.

**Precision mixed-signal microcontrollers** incorporate 12-bit or higher resolution ADCs and DACs. Sigma-delta ADCs can even have a resolution of 24-bits and a PGA can provide software programmable gains in the range of 1 to 128.

**High-speed microcontrollers** execute most of their instructions within a single clock cycle and can operate at frequencies from about 25 MHz to several hundred MHz.

According to the bus width there are **8-bit**, **16-bit and 32-bit microcontroller** families. 8-bit microcontrollers typically consume less power, while 32-bit microcontrollers have more processing power.

**Industrial and automotive microcontrollers** operate at a full industrial temperature range of -40 °C to 85 °C. The internal peripherals have stricter specifications to provide additional reliability under various conditions, and accuracy of the internal oscillator is better than 1% over the full operating temperature range. These microcontrollers typically have industrial or automotive communication peripherals like CAN buses or LIN buses.

**Secure microcontrollers** are used in security-sensitive applications including electronic banking and payment, application protection, communication and more. These microcontrollers offer protection of code and data, prevent reverse engineering, tampering, data monitoring and physical attacks. Hardware cryptographic modules, random number generators, fast data and code encryption are implemented to support secure applications.

## 2 Architecture and properties of the C8051Fxxx microcontroller family

C8051Fxxx microcontrollers developed by Silicon Laboratories [1, 2] are among the most powerful modern derivatives of the popular MCS-8051 MCU introduced by Intel. A short summary of these devices follows.

#### 2.1 8051 microcontrollers

The 8051 or MCS-51 family of 8-bit Harvard architecture microcontrollers were developed by Intel in the eighties for embedded applications. Their easily upgradable architecture proved successful, became a standard for many manufacturers and several derivatives are still popular on the market due to their ease of use and carefully designed peripheral handling.

The 8051 family can be easily programmed. There are many free and professional development tools, so the 8051 microcontrollers can be used by practiced experts, lecturers, students and hobbyists at the same time. Many source code examples are available to solve various problems and the manufacturers provide very useful application notes, knowledge base and user forums.

Manufacturers include Silicon Laboratories, Maxim/Dallas, Analog Devices, Atmel and NXP (formerly Philips).

Very wide ranges of speed, code and data memory size, analogue and digital peripherals, power requirement are provided by the C8051Fxxx family developed by Silicon Laboratories. The 1 MIPS peak performance of the original 8051 microcontroller has been upgraded up to 100 MIPS peak speed and the integrated flash memory, debug interface and very rich set of analogue and digital peripherals make the C8051Fxxx family a good choice for various applications.

The chips can have sizes of 2 mm  $\times$  2 mm (10 pins) to 16 mm  $\times$  16 mm (100 pins).

#### 2.2 The C8051Fxxx microcontroller family

The maximum clock frequency of the C8051Fxxx microcontrollers is in the range of 25 MHz to 100 MHz. Slower clock speeds are allowed, practically down to DC, so no minimum is specified. The frequency of the internal oscillator is programmable, so the user can choose low power operation at low frequencies, while higher processing speeds can be achieved at the expense of higher power consumption. For example, the C8051F410 processor can be operated at 50 MHz, when the core supply current is about 15 mA, while at 32 kHz the device draws less than 20  $\mu$ A from the supply rail, allowing long lasting operation from a battery.

The size of on-chip flash memory available varies from 2 kbyte to 128 kbyte, while the internal RAM can store 256 to 8448 bytes of data. The flash memory contains the code and may also be written by the code to support non-volatile data storage.

The C8o51Fxxx microcontrollers can have up to six 16-bit timers and a programmable counter array with 6 independent channels. Some devices include a real-time clock with battery backup power option.

Communication peripherals include UARTs,  $I^2C/SMBus$ , SPI, USB, CAN, LIN serial interfaces and the parallel external memory interface that also supports the connection of fast external ADCs, DACs and more.

From 6 to 64 GPIO pins are available with configurable output driving options (open-drain with or without internal pull-up and push-pull mode).

The C8051Fxxx family provides high-performance analogue peripherals. ADC resolutions from 10 to 12 bits with sample rates from 100 kHz to 200 kHz are common, while the C8051F06x devices incorporate two independent 1-MHz 16-bit ADCs, and the C8051F35x microcontroller has an 8-channel 24-bit ADC with programmable-gain amplifier to resolve sub- $\mu$ V signals. Some devices have a 32-channel multiplexer before their ADCs, and DACs with resolutions of 8 to 12 bits are also available. The list of analogue peripherals may also include up to 3 comparators with programmable response time and hysteresis.

The company provides several development tools including a free integrated development environment that supports the use of the popular open-source Small Device C Compiler (SDCC). A configuration wizard application helps much in configuring the peripherals properly by generating even the source code (assembly or C).

Hardware development platforms are also available. There are simple and full-featured development kits for almost all C8051Fxxx processors.

#### 2.3 The CIP-51 architecture

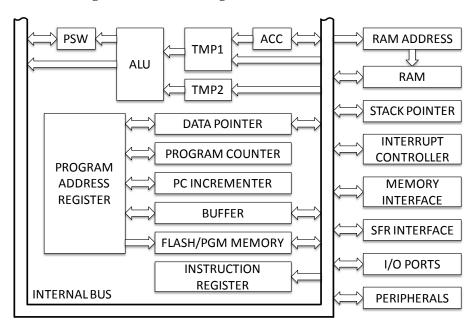

The Silicon Laboratories C8051Fxxx microcontrollers have the so-called CIP-51 architecture. The simplified block diagram is shown in Figure 2.1.

Figure 2.1. A simplified CIP-51 architecture.

The architecture is closely matched with the original 8051 architecture developed by Intel; code compatibility is provided. The main improvements include much faster instruction execution, integrated flash memory and larger integrated RAM.

In the following the main features of the architecture will be discussed.

#### 2.3.1 Registers

The following table summarises the 8-bit registers, with short descriptions and the reset values. The registers can be used in several instructions. The accumulator (A or ACC) holds

the result of arithmetic and logic operations and the program status word (**PSW**), and contains several flags modified by operations. Additional registers support indirect addressing and stack handling. Instructions typically execute faster when the operands are registers.

| Register |                                                                            | Reset value   |                                                                        |                   |                 |   |  |

|----------|----------------------------------------------------------------------------|---------------|------------------------------------------------------------------------|-------------------|-----------------|---|--|

| A, ACC   | accumulator                                                                | , ALU result  |                                                                        |                   |                 | 0 |  |

| В        | general-purp<br>division                                                   | oose register | and register f                                                         | or multiplication | n and           | 0 |  |

| R0.–R7   | general-purpose registers, R0 and R1 are also used in indirect addressing  |               |                                                                        |                   |                 | 0 |  |

|          | Bit 7: <b>CY</b>                                                           | carry bit (se | carry bit (set by addition or subtraction, <i>ADDC</i> , <i>SUBB</i> ) |                   |                 |   |  |

|          | Bit 6: AC                                                                  | auxiliary ca  | 0                                                                      |                   |                 |   |  |

|          | Bit 5: <b>F0</b>                                                           | user flag     | 0                                                                      |                   |                 |   |  |

| PSW      | Bit 4: <b>RS1</b>                                                          |               | R0-R7 at                                                               | R0-R7 at          | R0-R7 at        | 0 |  |

|          | Bit 3: <b>RS0</b>                                                          |               | 10: 0x10                                                               | 11: 0x18          | 0               |   |  |

|          | Bit 2: <b>OV</b>                                                           | overflow (see | 0                                                                      |                   |                 |   |  |

|          | Bit 1: <b>F1</b>                                                           | user flag     | 0                                                                      |                   |                 |   |  |

|          | Bit 0: PAR                                                                 | parity bit: 1 | 0                                                                      |                   |                 |   |  |

| DPH, DPL | <b>DPTR</b> , data pointer, used in 16-bit indirect code or RAM addressing |               |                                                                        |                   | 0               |   |  |

| SP       | stack pointer<br>push/pop ins                                              | •             | / subroutine a                                                         | and interrupt ro  | outine calls or | 7 |  |

#### 2.3.2 Special function registers

The special function registers (SFRs) are used to access the peripherals and some registers. For example, **ACC** is the same as **A** (accumulator); therefore, it can be accessed as an SFR or as a register. This allows the accumulator to be used in some instructions when registers cannot be used (like *push* and *pop*, see later)

SFRs can be accessed by direct addressing instructions, where the address falls in the range of **0x80–0xFF**. Therefore, SFRs can be thought of as memory-mapped registers; the program can read or write their content as if they were in the RAM.

The following table shows the standard 8051 SFR registers.

| Address | 0    | 1    | 2   | 3   | 4   | 5   | 6 | 7 |

|---------|------|------|-----|-----|-----|-----|---|---|

| 0xF8    |      |      |     |     |     |     |   |   |

| 0xF0    | В    |      |     |     |     |     |   |   |

| 0xE8    |      |      |     |     |     |     |   |   |

| 0xE0    | ACC  |      |     |     |     |     |   |   |

| 0xD8    |      |      |     |     |     |     |   |   |

| 0xD0    | PSW  |      |     |     |     |     |   |   |

| 0xC8    |      |      |     |     |     |     |   |   |

| 0xC0    |      |      |     |     |     |     |   |   |

| 0xB8    | IP   |      |     |     |     |     |   |   |

| 0xB0    | P3   |      |     |     |     |     |   |   |

| 8Ax0    | IE   |      |     |     |     |     |   |   |

| 0xA0    | P2   |      |     |     |     |     |   |   |

| 0x98    | SCON | SBUF |     |     |     |     |   |   |

| 0x90    | P1   |      |     |     |     |     |   |   |

| 0x88    | TCON | TMOD | TL0 | TH0 | TL1 | TH1 |   |   |

| 0x80    | P0   | SP   | DPL | DPH |     |     |   |   |

Note that SFRs in column 0 are bit addressable.

The SFRs listed in the table are the following (some of them will be discussed in the next chapters):

- **P0**, **P1**, **P2** and **P3** are the port input/output SFRs that are associated with the pins of the microcontroller. For example, the byte written to **P0** determines the logic signal on the 8 pins corresponding to **P0**. The programmer must be careful: for example, writing 1 to **P0** sets the least significant bit but will clear all the other 7 bits. Since the **P0** register is bit addressable, a single bit can be written or read without affecting the other bits. For example, setting **P0.0** sets the least significant bit only; all the other bits remain unchanged. Bit addressing is also useful for accessing a single bit of the status and other registers where the individual bits have special meanings.

- **ACC** and **B** provide **SFR** access to the accumulator and to the B register.

- **PSW** is the program status word. Its individual bits are accessible using bit addressing. For example, **PSW.7** is the carry bit.

- **SP** is the stack pointer.

- **DPL** and **DPH** are the low- and high-order bytes of the data pointer **DPTR**.

- **IE** and **IP** are the interrupt enable and priority registers. Their individual bits are accessible using bit addressing.

- TCON, TMOD, TL0, TH0, TL1 and TH1 are used to access and control the Timer o and Timer 1 peripherals.

**SCON** and **SBUF** are associated with the serial port communication peripheral.

#### 2.3.3 Memory structure

8051 processors have Harvard architecture; they have separate memory for code and data. The code memory can store constant data, so it can be used as a read-only data memory. Two types of RAM are available: internal and external. The internal RAM size is 256 bytes, while the external RAM is addressed by a 16-bit pointer, so the maximum size is 64 kbyte.

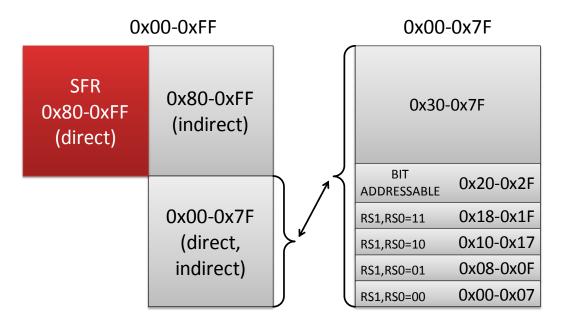

Figure 2.2 shows the internal RAM structure. The first 128 bytes (from 0x00-0x7F) can be accessed by direct or indirect addressing. The general-purpose registers occupy 8 bytes at the location defined by the **RS0** and **RS1** bits of the **PSW** register. The 16-byte space at address 0x20-0x2F is bit addressable, so 128 individual bit variables can be used here.

Figure 2.2. Internal memory structure of CIP-51 microcontrollers.

The SFR registers are mapped to the upper 128 bytes of the address space. SFRs are accessed by direct addressing; otherwise, the upper 128 bytes of the internal RAM can be used. Note that since stack handling is based on indirect addressing by the stack pointer, the upper 128 bytes of RAM can also be used as stack space. Upon reset, the stack pointer has the value of 7 and increases from there. However, it is best to set the initial value of the stack pointer (**SP**) to the first free location of data memory, just above the variables. In this case, all free memory is available as stack.

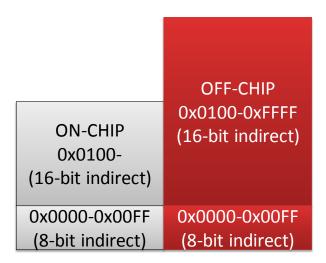

The external RAM (XRAM) was originally provided by SRAM chips, but modern C8o51Fxxx processors integrate a certain amount (up to 8192 bytes) of this kind of RAM. XRAM memory can only be accessed by 16-bit indirect addressing using the **DPTR** pointer (**DPH** and **DPL** registers).

XRAM at oxoo-oxFF can also be accessed by 8-bit indirect addressing using either the **R0** or the **R1** register.

Since off-chip memory can be slower than the on-chip memory, the control timing (data setup and hold time, write/read pulse width, etc.) can be set by dedicated SFR registers.

Figure 2.3 shows the XRAM arrangement in C8051Fxxx processors. The processor can be configured to access the on-chip memory only, the off-chip memory only or on-chip only if it is available and off-chip otherwise. The 8-bit addressable space can also be moved to another 256-byte page. Note that not all C8051Fxxx processors support off-chip memory.

Figure 2.3. External memory structure of CIP-51 microcontrollers.

#### 2.3.4 Addressing modes

Data can be accessed in different ways depending on its location (register, memory or code) and on the so-called addressing mode. The following table summarises the four possible addressing modes and shows examples.

| Addressing mode       | MNEMONIC example           | Description                                                                                                                       |

|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| register              | MOV A, B                   | $A \leftarrow B$ , copy the content of B to A                                                                                     |

| immediate<br>constant | MOV A, #10                 | A ← 10 (value), copy the value 10 to A                                                                                            |

| direct                | MOV A, 10<br>MOV A, P0     | A ← byte in internal RAM at address 10 A ← bits at port P0 (SFR access)                                                           |

| indirect              | MOV A, @R0<br>MOVX A,@DPTR | A $\leftarrow$ byte in internal RAM at address pointed to by R0 A $\leftarrow$ byte in external RAM at address pointed to by DPTR |

#### 2.3.5 Instructions

A brief summary of the available instructions are given in the following. Instructions are classified into groups and tables summarise their function and the flags affected by them.

2.3.5.1 Arithmetic operations

| MNEMONIC              | OPERATION                     | ADDR | ADDRESSING |       | FLAG | FLAG |    |    |   |

|-----------------------|-------------------------------|------|------------|-------|------|------|----|----|---|

|                       |                               | DIR  | IND        | REG   | IMM  | CY   | AC | OV | Р |

| ADD A, <byte></byte>  | A←A+ <byte></byte>            | ✓    | ✓          | ✓     | ✓    | ✓    | ✓  | ✓  |   |

| ADDC A, <byte></byte> | A←A+ <byte>+C</byte>          | ✓    | ✓          | ✓     | ✓    | ✓    | ✓  | ✓  |   |

| SUBB A, <byte></byte> | A←A- <byte>-C</byte>          | ✓    | ✓          | ✓     | ✓    | ✓    | ✓  | ✓  |   |

| INC A                 | A←A+1                         |      |            |       |      |      |    |    |   |

| INC <byte></byte>     | <byte>←<byte>+1</byte></byte> | ✓    | ✓          | ✓     |      |      |    |    |   |

| INC DPTR              | DPTR←DPTR+1                   |      | only       | DPTR  |      |      |    |    |   |

| DEC A                 | A←A–1                         |      | on         | ly A  |      |      |    |    |   |

| DEC <byte></byte>     | <byte>←<byte>−1</byte></byte> | ✓    | ✓          | ✓     |      |      |    |    |   |

| MUL AB                | B:A←BxA                       |      | only A     | and B |      | 0    |    | ✓  |   |

| DIV AB                | A←Int[A/B]<br>B←Mod[A/B]      |      | only A     | and B |      | 0    |    | ✓  |   |

| DA A                  | Decimal Adjust                |      | on         | ly A  |      | ✓    |    |    |   |

2.3.5.2 Logic operations

| MNEMONIC                   | OPERATION                             |     | FLAG |     |     |   |

|----------------------------|---------------------------------------|-----|------|-----|-----|---|

|                            |                                       | DIR | IND  | REG | IMM | Р |

| ANL A, <byte></byte>       | A←A AND <byte></byte>                 | ✓   | ✓    | ✓   | ✓   | ✓ |

| ANL <byte>,A</byte>        | <byte>←<byte> AND A</byte></byte>     | ✓   |      |     |     |   |

| ANL<br><byte>,#data</byte> | <byte>←<byte> AND #data</byte></byte> | ✓   |      |     |     |   |

| ORL A, <byte></byte>       | A←A OR <byte></byte>                  | ✓   | ✓    | ✓   | ✓   | ✓ |

| ORL <byte>,A</byte>        | <byte>←<byte> OR A</byte></byte>      | ✓   |      |     |     |   |

| ORL<br><byte>,#data</byte> | <byte>←<byte> OR #data</byte></byte>  | ✓   |      |     |     |   |

| XRL A, <byte></byte>       | A←A XOR <byte></byte>                 | ✓   | ✓    | ✓   | ✓   | ✓ |

| XRL <byte>,A</byte>        | <byte>←<byte> XOR A</byte></byte>     | ✓   |      |     |     |   |

| XRL<br><byte>,#data</byte> | <byte>←<byte> XOR #data</byte></byte> | ✓   |      |     |     |   |

2.3.5.3 Accumulator manipulation

| MNEMONIC | OPERATION                       | ADDRESSING |    | FL | AG |   |

|----------|---------------------------------|------------|----|----|----|---|

|          |                                 |            | CY | AC | OV | Р |

| CRL A    | A ← 00H                         | only A     |    |    |    | ✓ |

| CPL A    | $A \leftarrow NOT A$            | only A     |    |    |    | ✓ |

| RL A     | Rotate ACC Left 1 bit           | only A     |    |    |    | ✓ |

| RLC A    | RLC A Rotate Left through Carry |            |    |    |    | ✓ |

| RR A     | Rotate ACC Right 1 bit          | only A     |    |    |    | ✓ |

| RRC A    | Rotate Right through Carry      | only A     |    |    |    | ✓ |

| SWAP A   | Swap Nibbles in A               | only A     |    |    |    | ✓ |

2.3.5.4 Bit-variable operations

| MNEMONIC   | OPERATION                    |

|------------|------------------------------|

| ANL C,bit  | C ← C AND bit                |

| ANL C,/bit | $C \leftarrow C$ AND NOT bit |

| ORL C,bit  | C ← C OR bit                 |

| ORL C,/bit | C ← C OR NOT bit             |

| MOV C,bit  | C ← bit                      |

| MOV bit,C  | bit ← C                      |

| CLR C      | C ← 0                        |

| CLR bit    | bit ← 0                      |

| SETB C     | C ← 1                        |

| SETB bit   | bit ← 1                      |

| CPL C      | C ← NOT C                    |

| CPL bit    | bit ← NOT bit                |

2.3.5.5 Data move operations

| MNEMONIC                      | OPERATION                           | ADDRESSING |     |     |     |  |  |

|-------------------------------|-------------------------------------|------------|-----|-----|-----|--|--|

|                               |                                     | DIR        | IND | REG | IMM |  |  |

| MOV A, <src></src>            | A ← <src></src>                     | ✓          | ✓   | ✓   | ✓   |  |  |

| MOV <dest>,A</dest>           | <dest> ← A</dest>                   | ✓          | ✓   | ✓   |     |  |  |

| MOV <dest>,<src></src></dest> | <dest> ← <src></src></dest>         | ✓          | ✓   | ✓   | ✓   |  |  |

| MOV DPTR,#data16              | DPTR ← 16-bit immediate constant    |            |     |     | ✓   |  |  |

| PUSH <src></src>              | SP ← SP+1<br>@SP ← <src></src>      | ✓          |     |     |     |  |  |

| POP <dest></dest>             | <dest> ← @SP<br/>SP ← SP-1</dest>   | ✓          |     |     |     |  |  |

| XCH A, <byte></byte>          | ACC and <byte> exchange data</byte> | ✓          | ✓   | ✓   |     |  |  |

| XCHD A,@Ri                    | ACC and @Ri exchange low nibbles    |            | ✓   |     |     |  |  |

2.3.5.6 External and code memory access

| MNEMONIC       | OPERATION          |

|----------------|--------------------|

| MOVX A,@Ri     | A ← XRAM @Ri       |

| MOVX @Ri,A     | XRAM @Ri ← A       |

| MOVX A,@DPTR   | A ← XRAM @DPTR     |

| MOVX @DPTR,A   | XRAM @DPTR ← A     |

| MOVC A,@A+DPTR | A ← code @(A+DPTR) |

| MOVC A,@A+PC   | A ← code @(A+PC)   |

#### 2.3.5.7 Jump and subroutine call

| MNEMONIC            | OPERATION                                                                                                                                                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JMP <addr></addr>   | Jump to <addr> PC ← <addr></addr></addr>                                                                                                                                                                                                                                          |

| JMP @A+DPTR         | Jump to A+DPTR PC ← A+DPTR                                                                                                                                                                                                                                                        |

| ACALL <addr></addr> | Call subroutine at 11-bit <addr> <math>PC \leftarrow PC+2</math> <math>SP \leftarrow SP+1</math> <math>@SP \leftarrow PC</math> lower order byte <math>SP \leftarrow SP+1</math> <math>@SP \leftarrow PC</math> higher order byte <math>PC \leftarrow <addr></addr></math></addr> |

| LCALL <addr></addr> | Call subroutine at 16-bit <addr> <math>PC \leftarrow PC+3</math> <math>SP \leftarrow SP+1</math> <math>@SP \leftarrow PC</math> lower order byte <math>SP \leftarrow SP+1</math> <math>@SP \leftarrow PC</math> higher order byte <math>PC \leftarrow <addr></addr></math></addr> |

### 2.3.5.8 Return from subroutines and interrupts

| MNEMONIC | OPERATION                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------|

| RET      | Return from subroutine $PC \leftarrow @(SP, SP-1)$ $SP \leftarrow SP-2$                                                         |

| RETI     | Return from interrupt $PC \leftarrow @(SP, SP-1)$ $SP \leftarrow SP-2$ restore the interrupt logic to accept further interrupts |

| NOP      | No operation                                                                                                                    |

2.3.5.9 Conditional jumps

| MNEMONIC                                      | OPERATION                      | ADDRESSING |     |     |     |  |

|-----------------------------------------------|--------------------------------|------------|-----|-----|-----|--|

|                                               |                                | DIR        | IND | REG | IMM |  |

| JZ <rel addr=""></rel>                        | Jump if A = 0                  |            | onl | у А |     |  |

| JNZ <rel addr=""></rel>                       | Jump if A !=0                  |            | onl | у А |     |  |

| DJNZ <byte>,<rel addr=""></rel></byte>        | Decrement and jump if not zero | ✓          |     | ✓   |     |  |

| CJNE A, <byte>,<rel addr=""></rel></byte>     | Jump if A != <byte></byte>     | ✓          |     |     | ✓   |  |

| CJNE <byte>,#data, <rel addr=""></rel></byte> | Jump if <byte> != #data</byte> |            | ✓   | ✓   |     |  |

| JC <rel addr=""></rel>                        | Jump if C = 1                  |            |     |     |     |  |

| JNC <rel addr=""></rel>                       | Jump if C = 0                  |            |     |     |     |  |

| JB bit, <rel addr=""></rel>                   | Jump if bit = 1                |            |     |     |     |  |

| JNB bit, <rel addr=""></rel>                  | Jump if bit = 0                |            |     |     |     |  |

| JBC bit, <rel addr=""></rel>                  | Jump if bit = 1; CLR bit       |            |     |     |     |  |

#### 2.3.6 Instruction timing and coding

The CIP-51 architecture executes most of the operations in 1 or 2 system clock cycles. Depending on the specific device, the system clock can have maximum frequencies from 25 MHZ to 100 MHz; therefore, the fastest instruction execution time can be as low as 10 ns. The following table shows the distribution of the cycle time for the available instructions. Note that processors operating at clock frequencies above 25 MHz may use pipelining (prefetching instructions into a fast buffer) due to flash code memory access time limitations. This means that the processor may stall for a few clock cycles in some cases (for example, when a jump or a branching occurs).

| cycles       | 1  | 2  | 2/4 | 3  | 3/5 | 4 | 5 | 4/6 | 6 | 8 |

|--------------|----|----|-----|----|-----|---|---|-----|---|---|

| instructions | 26 | 50 | 5   | 10 | 7   | 5 | 2 | 1   | 2 | 1 |

The CISC architecture of the 8051 processors allows instructions to be coded using 1, 2 or 3 bytes. The first byte is associated with the type of the instruction, while the remaining one or two identify the operands. A few examples are shown in the next table.

| instruction               | 1. byte   | 2. byte     | 3. byte   | cycles |

|---------------------------|-----------|-------------|-----------|--------|

| ADD A, Rn                 | 0010 1nnn |             |           | 1      |

| ADD A, #10                | 0010 0100 | 0000 1010   |           | 2      |

| ANL 15,#10                | 0101 0011 | 0000 1111   | 0000 1010 | 3      |

| DIV AB                    | 1000 0100 |             |           | 8      |

| JZ <rel address=""></rel> | 0110 0000 | rel address |           | 2/4    |

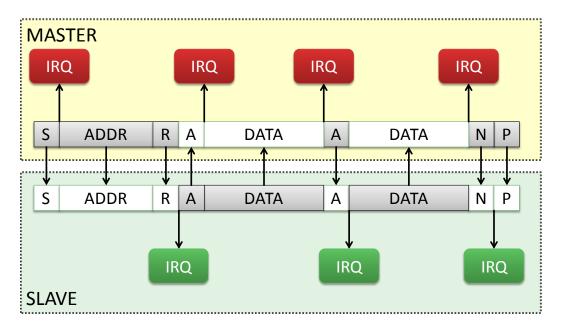

#### 2.3.7 Interrupt handler

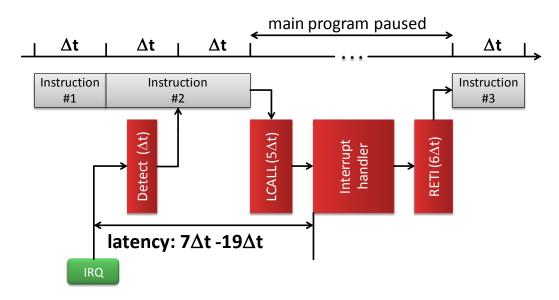

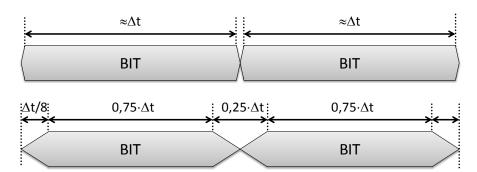

Event handling is one of the most important aspects of embedded programming. Events can be generated by peripherals such as timers, communication ports, and analogue-to-digital converters and also by changes of external signals. In the 8051 environment, events can generate interrupts, which can be serviced by subprograms. If an event occurs, a flag is set (which can even be polled by software) and an associated interrupt routine is called if enabled. The interrupt mechanism is visualised in Figure 2.4. When the event occurs, the system detects this within the system clock cycle time  $\Delta t$  (the reciprocal of the system clock frequency). Upon completion of the currently running instruction (which can take from 1 to 8 cycles; see the previous chapter), an **LCALL** instruction is executed and the program jumps to the interrupt service routine. After processing, a **RETI** instruction is executed to return to the main program and restore the interrupt logic to accept further interrupts. One can easily see that the time elapsed from the event to the execution of the first instruction of the interrupt handler requires a minimum latency time and has some uncertainty as well.

Figure 2.4. Interrupt mechanism. The interrupt latency time varies from 7 to 19 system clock periods.

It is very important to keep this in mind, since in a real-time application it can cause problems. For example, if a periodic interrupt is used to generate a square wave, this causes some fluctuation of the switching times, which should be considered, especially when switching times are short. For example, if a 100-kHz square wave is to be generated by a timer interrupt routine, the routine must be called 200000 times per second to change the signal state at every 5  $\mu$ s. At a system clock frequency of 25 MHz, the clock period is 40 ns, so the latency time can vary from 7·40 ns to 19·40 ns, resulting in an uncertainty of (19-7)·40 ns=480 ns. This can cause a maximum error of 9.6% in the 5- $\mu$ s switching time.

The main program can be interrupted at any time, even during a task requiring multiple instructions. This means that all temporary variables and register content modified by the interrupt service routine must be saved at the beginning of the interrupt handling routine and must be restored upon return to the main program. Also note that the peripheral state or the input/output can also be changed during interrupt handling, which also needs careful attention.

If an interrupt service routine is running, another request can only be serviced if it has higher priority. Only two priority levels are provided, so no further interrupts can be serviced. The priority of the interrupts is defined by the bits of the **IP**, **EIP1** and **EIP2** registers. Correspondingly, there are only two priority levels: normal and high. If more interrupts are detected simultaneously, the higher priority interrupt will be serviced first. Since the interrupt flag set by the event can be cleared only when the associated interrupt routine is called, no interrupts are lost if multiple requests are detected or the request occurs during the servicing of another one. Of course, if a request is generated two or more times without servicing, only the last request can be serviced.

Interrupt sources are associated with a number that also defines priority (lower number means higher priority). The execution address of the interrupt routines is fixed and only 8 bytes are available up to the next address. Therefore, longer routines are located elsewhere and only a jump to that space is needed here.

A few interrupt flags are automatically cleared by the hardware when the service routine is called; all others must be cleared by the software – otherwise, the request will remain active and will be serviced continuously.

Interrupts can be individually enabled and disabled using the bits of the **IE**, **EIE1** and **EIE2** registers. **IE.7** (which can also be accessed as the SFR bit **EA**) is a global enable bit. Note that if an interrupt is enabled, it must have an interrupt handler code; otherwise, the processor can go into an uncertain state.

The interrupt sources available on C8051F410 processors are listed in the following table.

|                           |                      | ٦      | bit        | bit          | Flag                       |                     |  |

|---------------------------|----------------------|--------|------------|--------------|----------------------------|---------------------|--|

| Source                    | Execution<br>Address | Number | Enable bit | Priority bit | name                       | Cleared by hardware |  |

| Reset                     | 0x0000               | -      |            |              | -                          | yes                 |  |

| /INT0 external            | 0x0003               | 0      | IE.0       | IP.0         | IE0                        | yes                 |  |

| Timer 0 overflow          | 0x000B               | 1      | IE.1       | IP.1         | TF0                        | yes                 |  |

| /INT1 external            | 0x0013               | 2      | IE.2       | IP.2         | IE1                        | yes                 |  |

| Timer 1 overflow          | 0x001B               | 3      | IE.3       | IP.3         | TF1                        | no                  |  |

| UART                      | 0x0023               | 4      | IE.4       | IP.4         | RI, TI                     | no                  |  |

| Timer 2 overflow          | 0x002B               | 5      | IE.5       | IP.5         | TF2H, TF2L                 | no                  |  |

| SPI0                      | 0x0033               | 6      | IE.6       | IP.6         | SPIF, WCOL,MODF,<br>RXOVRN | no                  |  |

| SMB0                      | 0x003B               | 7      | EIE1.0     | EIP1.0       | SI                         | no                  |  |

| smaRTClock                | 0x0043               | 8      | EIE1.1     | EIP1.1       | ALRM, OSCFAIL              | no                  |  |

| ADC0 Window<br>Comparator | 0x004B               | 9      | EIE1.2     | EIP1.2       | AD0WINT                    | no                  |  |

| ADC0 End of Conversion    | 0x0053               | 10     | EIE1.3     | EIP1.3       | AD0INT                     | no                  |  |

| Programmable Counter Array | 0x005B | 11 | EIE1.4 | EIP1.4 | CF, CCFn (up to six flags) | no |

|----------------------------|--------|----|--------|--------|----------------------------|----|

| Comparator 0               | 0x0063 | 12 | EIE1.5 | EIP1.5 | CP0FIF, CP0RIF             | no |

| Comparator 1               | 0x006B | 13 | EIE1.6 | EIP1.6 | CP1FIF, CP1RIF             | no |

| Timer 3 overflow           | 0x0073 | 14 | EIE1.7 | EIP1.7 | TF3H, TF3L                 | no |

| Voltage regulator dropout  | 0x007B | 15 | EIE2.0 | EIP2.0 | -                          | no |

| Port match                 | 0x0083 | 16 | EIE2.1 | EIP2.1 | -                          | no |

#### 3 Assembler and C programming

Programming 8051 microcontrollers requires special attention due to limited processing power, small memory space and the direct access of peripherals. No operating system is used in most cases; therefore, the programmer must take care of everything that the microcontroller does. The programmer must have extensive knowledge about the hardware, including memory types, instructions, SFRs, the interrupt handler and digital and analogue peripherals.

Simple programs can be written in assembler, but C is recommended for general-purpose code development. Although code optimisations are done by the C compiler, some fragments of code can be further enhanced by mixing assembler and C. C compilers allow inserting assembly code in C and C and assembly code can work on the same variables. C programmers can write efficient embedded code only if they know assembler as well.

#### 3.1 SDCC C compiler

There are many 8051 C Compilers on the market. The most popular professional compiler is the KEIL C51 [3] and there exists an open-source alternative called Small Device C Compiler (SDCC) [4]. The free availability, good quality and the detailed documentation of SDCC make it an ideal tool to use in education. Here only the most important additions to C are mentioned that are needed to use the features of the 8051 processor.

Variables can be placed in different memory types; for this purpose, the compiler supports the declaration of storage classes:

```

__data unsigned char x; // internal RAM

__xdata unsigned char x; // external RAM

__idata unsigned char x; // internal indirectly addressable RAM

__pdata unsigned char x; // 8-bit addressed external RAM

__code unsigned char x=3; // constant in code memory

__bit b; // bit addressable RAM

__sfr __at 0x80 PO; // SFR byte

__sbit __at 0xD7 CARRY; // SFR bit

__xdata __at (0x4000) unsigned char x[16]; // external RAM, absolute address

__code __at (0x7f00) char Msg[] = "Message"; // code memory, absolute address

__bit __at (0x80) GPIO_0; // bit, absolute address

```

Inserting assembly into C can be done using the <u>asm</u> and <u>endasm</u> directives:

```

unsigned char x;

// beginning of assembly code fragment

asm

clr a

/* C style comment */

mov R0,#0 // P0, C++ style comment

mov R1,#0x80 // C style hexadecimal constant

mov a,R2

// copy the content of R2 register to accumulator

// accessing x declared in C

mov x,a

jz L1

// use of a label

mov R0,#0

// clear register R0

mov R1,#1

// load 1 into register R1

endasm;

// end of assembly code fragment

```

The variable types are listed in the following table.

| type             | width<br>(bits) | default  | signed range               | unsigned range                                                       |

|------------------|-----------------|----------|----------------------------|----------------------------------------------------------------------|

| bit              | 1               | unsigned | -                          | 0,1                                                                  |

| char             | 8               | signed   | -128–127                   | 0–255                                                                |

| short            | 16              | signed   | -32768–32767               | 0–65535                                                              |

| int              | 16              | signed   | -32768–32767               | 0–65535                                                              |

| long             | 32              | signed   | -2147483648<br>+2147483647 | 0-4294967296                                                         |

| float<br>IEEE754 | 32              | signed   |                            | 1.175494351 · 10 <sup>-38</sup> ,<br>3.402823466 · 10 <sup>+38</sup> |

| pointer          | 8-24            | generic  |                            |                                                                      |

Most of the variable types are the same as in standard C, but due to the limited resources, there are some exceptions. For example, the SDCC compiler allows defining bit variables using the \_\_bit keyword. The variable can be placed in the bit addressable memory space, optimising memory usage. Floating-point arithmetic is supported; however, only single precision 4-byte wide float type variables can be used. This is fine in most embedded applications due to its 6-7 digits of precision. Double precision is not available, because it would take a long execution time and significantly longer code.

Generic pointers are rather special, since the 8051 microcontroller uses several different memory types. The 3-byte wide generic pointer defines the address in two bytes and the memory type (internal RAM, external RAM or code memory) on the third byte. Of course, the programmer can declare a pointer that points explicitly to an internal memory location. This pointer is stored in a single byte since only 256 different locations are possible.

Microcontroller programming often requires the manipulation of bits. Here are two simple examples:

```

x = x & \sim (1 << 3); // clearing a bit x = x | (1 << 3); // setting a bit

```

Working with integer numbers that are not 8, 16 or 32 bits long is also common. Left or right shifting may be required, but care must be taken concerning signed and unsigned numbers, since the behaviour of the shift operator is different for signed and unsigned numbers. For example, to handle a 2s complement 12-bit number (the four most significant bits are in ADCH and the eight least significant bits are in ADCL), one may use the following code:

```

short x; // define a signed 16-bit integer variable x = (ADCH << 12) + (ADCL << 4); // left justified x = ((signed short) (ADCH << 12) >> 4) + ADCL; // right justified

```

In most cases, unsigned integers are used for the data of the peripherals (such as counter value or ADC value). The programmer should always declare the variable as unsigned if it contains an unsigned number. However, the use of negative constants can help in some cases, especially when calculating the value used in timer programming (see Chapter 5):

```

unsigned short x; // define an unsigned 16-bit integer variable x = -100; // this is equivalent to 65536-100, i.e. 65436

```

Note that 65536 cannot be represented by an unsigned short variable and long arithmetic would take more time and longer code.

#### 3.2 Interrupt programming in assembler

A simple assembler interrupt handler example code is listed below. At the beginning, the registers in use are pushed onto the stack and restored at the end of the routine. The interrupt pending flag (in this example RI) is cleared. Note the use of assembler-style comments.

If the **R** registers are used, they must be saved and then restored as well. However, the 8-byte register bank can be moved to four memory locations; therefore, the interrupt routine can use one bank while the main code uses another bank.

```

push PSW ; status register to the stack

mov PSW,#8; use register bank #1

; use R registers here

pop PSW ; PSW and the register bank selection is restored here

```

The following complete assembler code illustrates the use of a timer interrupt to make an LED blink. The system clock after reset for the C8051F410 processor is 191406 Hz, and its 16-bit Timer 2 runs with 1/12 of this rate by default: 191406/12 Hz  $\approx 15950$  Hz. Since the interrupt occurs when the 16-bit timer overflows, 15950 steps are needed to reach  $2^{16}$ =65536 in order to wait 1 second before overflow. Therefore, the initial value of the timer should be set to 65536-15950 = 49586 = 0xC1B2, and this value will be reloaded upon overflow automatically. This way, a periodic interrupt will be generated every second. Note that the detailed description of the peripherals can be found in the following chapters.

```

$include (C8051F410.INC); load the definitions used for the C8051F410 MCU

LED

EQU P0.2

; the LED is connected to bit 2 of port 0.

CSEG at 0000h

jmp Main

; reset, jump to the label 'Main'

ORG 002Bh

; Timer 2 interrupt location

anl TMR2CN, #07Fh

; clear interrupt flag

; complement LED

cpl LED

; return from interrupt

reti

Main:

anl PCAOMD, #OBFh ; switch watchdog off

mov PCAOMD, #000h; switch watchdog off

#040h ; enable the crossbar to allow input and output

mov TMR2RLL, #0B2h ; set the Timer 2 reload register (low and high bytes)

mov TMR2RLH, #0C1h ; to provide 1-Hz interrupt rate

```

```

mov TMR2L, #0B2h ; Timer 2 counter initial value

mov TMR2H, #0C1h ; is the same as the reload value

mov TMR2CN, #004h ; Start Timer 2 now

mov IE, #0A0h ; enable global interrupts and Timer 2 interrupt

jmp $ ; repeat forever, interrupt routine will blink the LED

END

```

#### 3.3 Interrupt handling in C

The SDCC C compiler for the 8051 family of processors supports interrupt programming. If a function is intended to be an interrupt handler, it must be declared accordingly. The programmer should use the <u>\_\_interrupt</u> keyword and include the number of the interrupt to identify which interrupt will be handled. For example:

```

void InterruptHandler(void) __interrupt 5

or using predefined constants

void InterruptHandler(void) interrupt INT TIMER2

```

This code defines an interrupt handler (no return value or input arguments can be defined) for the Timer 2 interrupt that is numbered as 5. The location of the **R0**—**R7** register bank can also be defined:

```

void InterruptHandler(void) __interrupt 5 _ using 1

```

where the number following <u>using</u> keyword defines which one of the four possible register banks are used (the default is o). This can help the compiler to generate faster code since saving/restoring the registers is not necessarily needed.

An interrupt handler can use local variables, which are initialised in any execution of the routine. A simple example is the use of temporary variables. However, in some cases a variable must retain its value after exiting from the interrupt handler routine. For example, if the code must count how many interrupts are generated, a counter value must be incremented each time the interrupt routine is called. This variable can be declared as a global variable just at the beginning of the code, but if it is used in the interrupt routine only, it is best to hide the variable from other parts of the code. In this case, the variable should be declared in the interrupt handler routine using the static keyword. The following example code toggles the state of an LED upon every hundredth Timer 2 overflow interrupt request. The static variable named 'counter' counts how many requests are detected, and if this number reaches 100, the LED is toggled. Since the counter value is only used in the interrupt routine, it can be declared within the scope of the routine. Note that the initialisation of the variable is done only when the program starts.

If a variable is used both in an interrupt routine and in other parts of the program then *it must be declared as* volatile:

The volatile keyword tells the compiler that the variable can be changed at any time, so it cannot be assumed to remain unchanged in a sequence of a few lines of computations. It is a typical error to get unexpected results due to missing volatile declarations.

There are several considerations to be kept in mind if both interrupts and regular code work on the same data. The main program may work on data in several assembler instructions that are hidden from the programmer. For example, checking the value of a 16-bit number needs several assembler instructions: the higher- and lower-order bytes must be separately checked – it is not an *atomic* operation. If an interrupt routine changes the value of this integer during this process, an unexpected error can occur. Therefore, non-atomic operations must be protected.

One solution is the use of critical blocks as shown below:

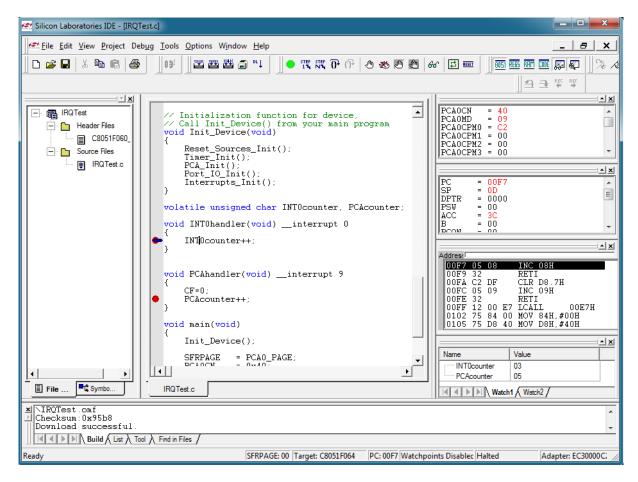

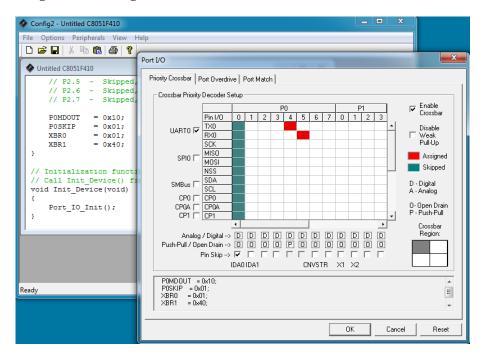

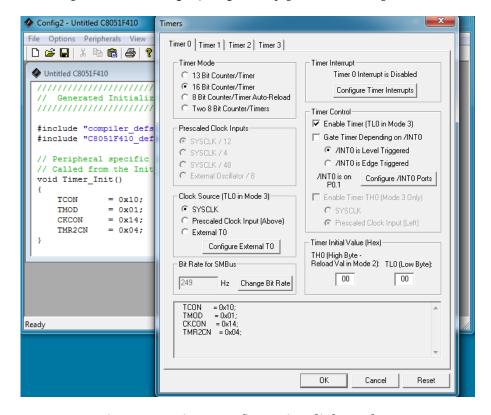

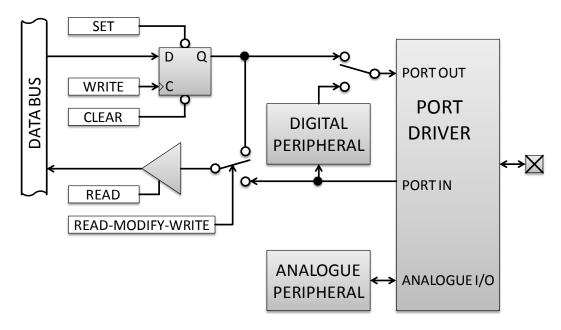

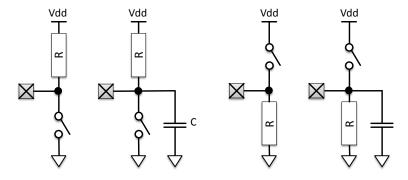

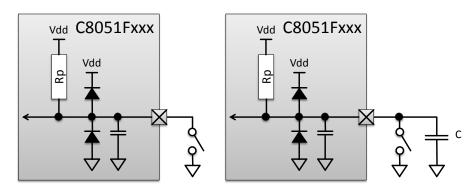

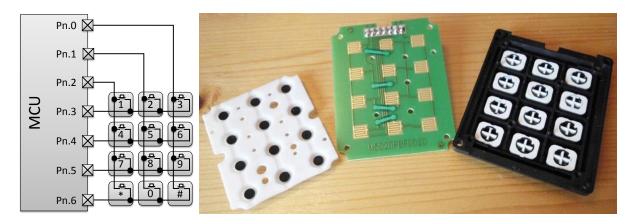

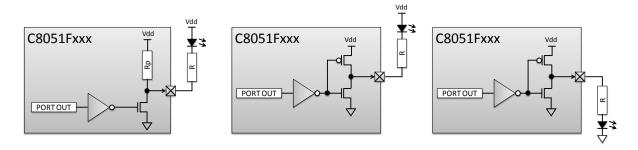

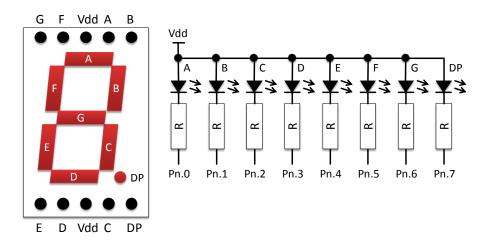

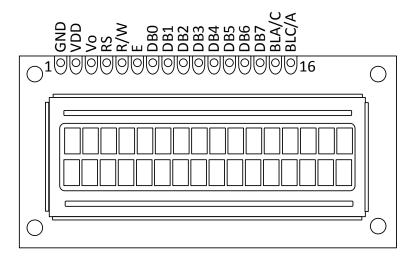

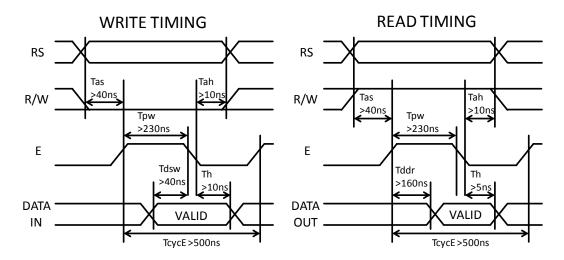

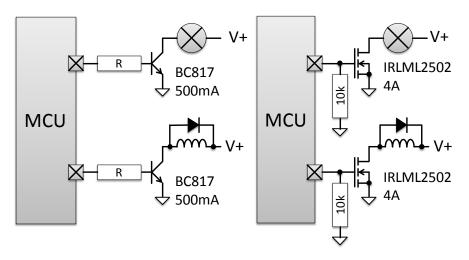

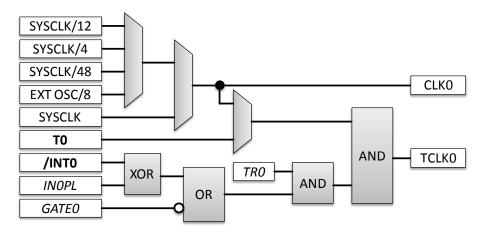

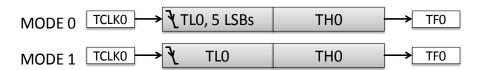

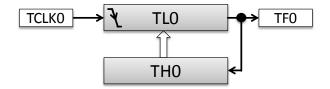

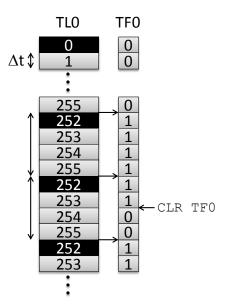

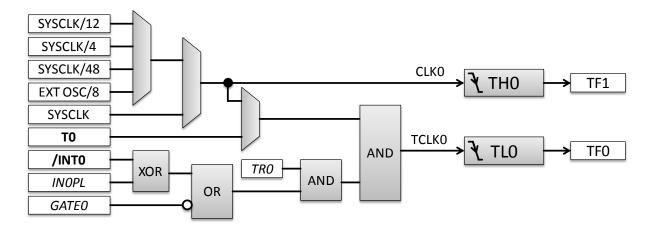

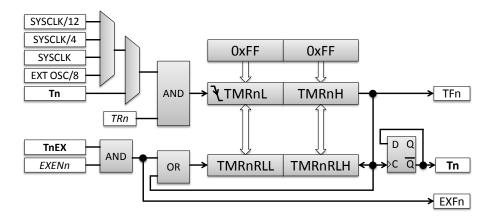

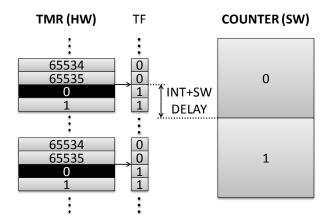

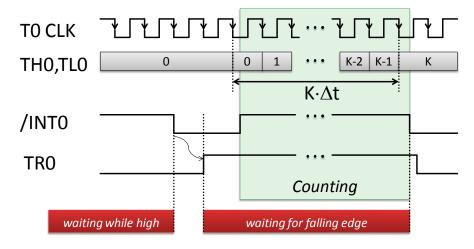

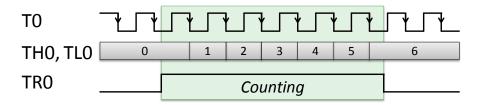

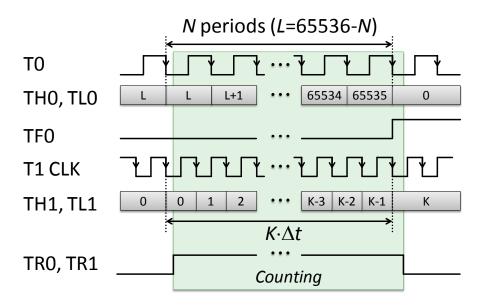

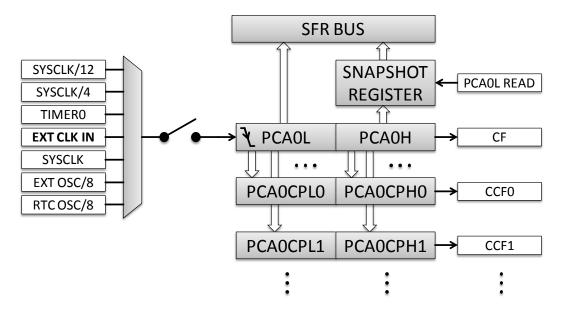

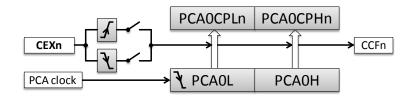

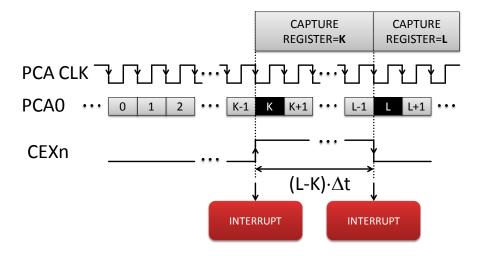

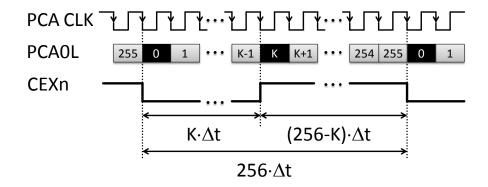

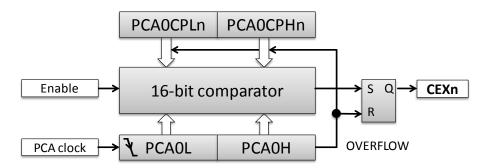

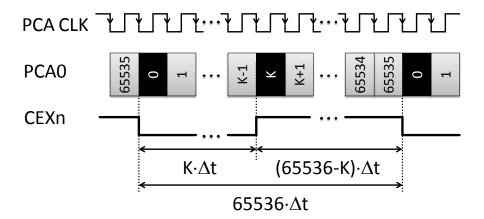

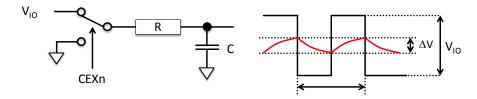

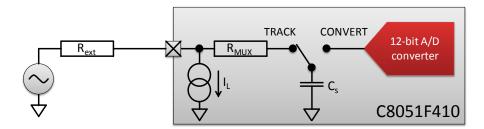

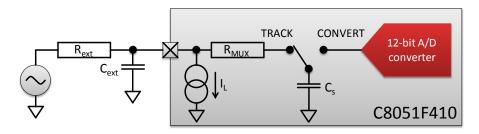

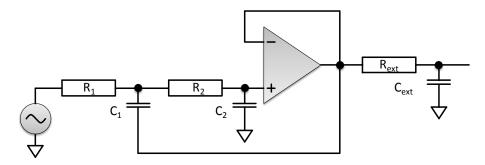

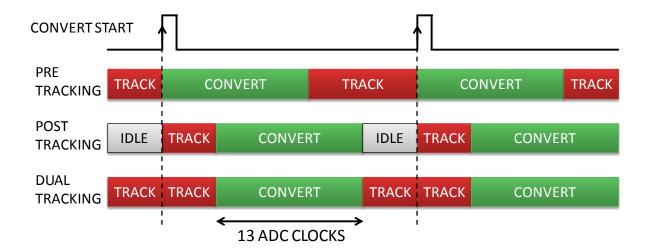

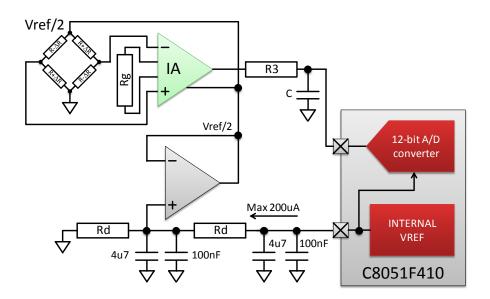

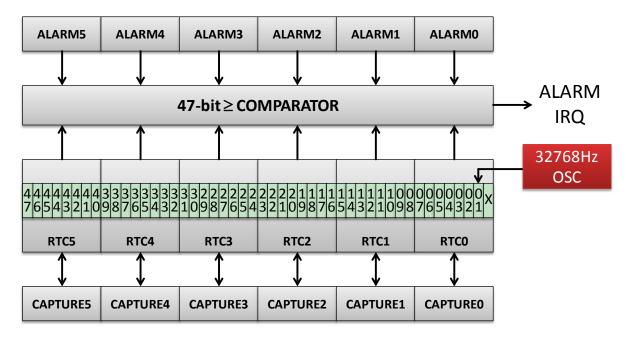

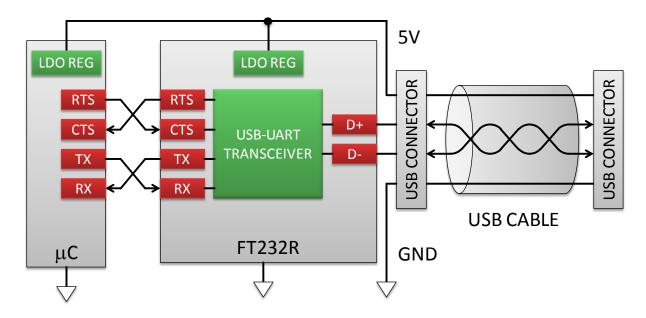

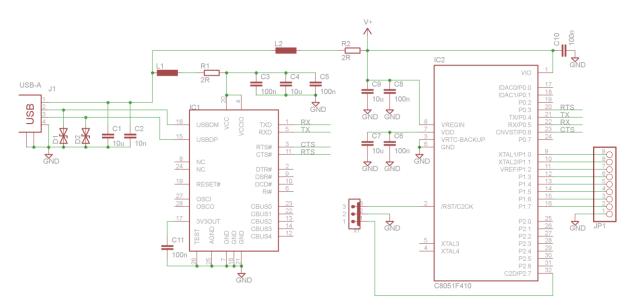

At the beginning of the critical block, the compiler disables interrupts (saves then clears **EA**) and at the end re-enables them if necessary (restores the value of **EA**); therefore, no interrupt can be executed within the critical block. Note that this may cause extra interrupt latency and even missing interrupts if the critical block needs too much time to complete.