# **Parallel Computing**

Dr. Juhász Zoltán

# 2014

A tananyag a TÁMOP-4.1.2.A/1-11/1-2011-0104 "A felsőfokú informatikai oktatás minőségének fejlesztése, modernizációja" c. projekt keretében a Pannon Egyetem és a Szegedi Tudományegyetem együttműködésében készült.

# **1 PREFACE**

Parallel computing is concerned with the execution of programs on computers having two or more processors. The main purpose of using multiple processors is to reduce the execution time of our programs. There has always been computational problems for which the computing power of a single processor is not sufficient. Traditionally, these problems have been the focus of parallel computing. There is a new, and much more practical reason for which parallel computing has become the new star of computing; and that is multi-core processors. We are in the multi-core era of computing; simply put, there are no computers with single-core processors any longer. The performance of processors is measured in the number of computing cores, not in clock frequency. A *sequential* program, written for one core will never be able to harness the performance of a multi-core processor. To maximally utilise these new processors, we need *parallel* programs that can be executed on different cores at the same time, in other words, *in parallel*.

In order for a program to be executable on a multiprocessor machine, it has to contain parts (subtasks or processes) that can be run on each processor in parallel. Our purpose in doing so is that by breaking the solution of a problem into sub-problems, we can decrease the overall execution time of the program. This concept is very similar, for instance, to the practice followed by the manufacturing industry, where a product is a result of components manufactured at the same time and then assembled in the most optimal way using several workers working in parallel.

The purpose of this book is to provide an introduction to this interesting topic and explore different aspects of parallel computation, such as multiprocessor computer architectures, parallel programming languages, parallel algorithms and applications. The amount of material that we could possibly cover in this book is enormous; therefore, the focus is only on introducing the most fundamental concepts, methods and programming techniques to students, which should prepare them for further, more specialised study of parallel computing subjects. It is always difficult to decide what topics to cover and what to leave out. Parallel computing is a much broader area than other fields of computer science; it affects each field of computing. Ideally, parallel computing should not be taught as a single course; rather, every topic of the computing curriculum should embrace and include parallel computing techniques and discuss them within the context of the field, for instance, present parallel architectures in Computer Architecture, parallel algorithms in Algorithms and Data Structure courses and so on. But until that happens, this book can help in guiding the reader through the key concepts.

2

The content of this book is strongly related to the structure and content of the Parallel Programming course regularly offered to BSc and MSc students at the Faculty of Information Technology at the University of Pannonia in Veszprem, Hungary. While the book is meant to be introductory, familiarity with the C and/or Java programming languages and knowledge of the fundamental concepts of computer architecture, operating systems, data structures and algorithms is expected. The chapters do not necessarily need to be read in the order they are presented in the book although, for readers not familiar with the topic, this might be the most suitable sequence.

While every care has been taken to create a correct manuscript, errors and omissions might be present. Any of these is the responsibility of the author but readers are more than welcome to send their feedback in order to improve the book.

Zoltan Juhasz

## **Table of Contents**

| 1              | Pref                                         | ace                                                                   | 2  |  |  |

|----------------|----------------------------------------------|-----------------------------------------------------------------------|----|--|--|

| 2 Introduction |                                              |                                                                       |    |  |  |

|                | 2.1 Parallel computing hardware and software |                                                                       |    |  |  |

| 3              | Para                                         | Parallel programming fundamentals12                                   |    |  |  |

|                | 3.1                                          | Computational performance                                             |    |  |  |

| 3.3 Par        |                                              | Supercomputing and parallel computing                                 |    |  |  |

|                |                                              | Parallel computers for the masses                                     | 16 |  |  |

|                |                                              | Solving problems in parallel                                          | 17 |  |  |

|                |                                              | 1 Data or geometric parallelism                                       |    |  |  |

|                |                                              | 2 Control or algorithmic parallelism                                  | 21 |  |  |

|                | 3.4.3                                        | 3 Farming parallelism                                                 | 26 |  |  |

|                | 3.5                                          | Parallel execution performance – the basics                           |    |  |  |

|                | 3.5.2                                        | 1 Suboptimal performance                                              |    |  |  |

|                | 3.6                                          | Creating and executing parallel programs                              |    |  |  |

|                | 3.7                                          | References                                                            |    |  |  |

| 4              | Para                                         | Parallel processing architectures                                     |    |  |  |

|                | 4.1                                          | Shared-memory computers                                               |    |  |  |

|                | 4.1.3                                        | 1 The operating mechanism of a single-bus shared-memory multicomputer |    |  |  |

|                | 4.1.2                                        | 2 The cache-based shared-memory multicomputer                         | 41 |  |  |

|                | 4.1.3                                        | Cache synchronisation (the cache coherency problem)                   | 42 |  |  |

|                | 4.1.4                                        | 4 Methods to provide cache coherence                                  | 43 |  |  |

|                | 4.1.                                         | 5 Crossbar-based shared memory architectures                          | 45 |  |  |

|                | 4.1.6                                        | 5 Switch-based shared memory architectures                            | 46 |  |  |

|                | 4.2                                          | Distributed-memory parallel computers                                 |    |  |  |

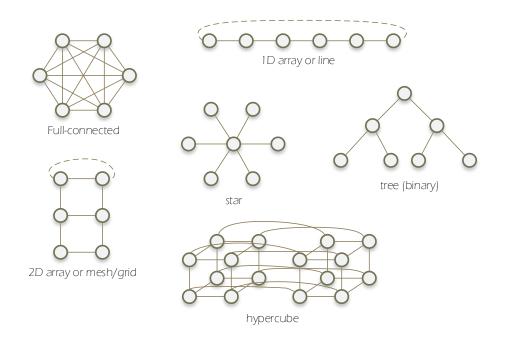

|                | 2.2.2                                        | Point-to-point interconnections                                       | 51 |  |  |

|                | 2.2.2                                        | 2 Comparing static topologies                                         |    |  |  |

|                | 4.2.2                                        | 1 Routing and communication in static networks                        | 53 |  |  |

|                | 2.2.3                                        | 3 Dynamic Interconnection Systems                                     | 57 |  |  |

|                | 4.3                                          | Multi-core processors                                                 | 59 |  |  |

|                | 4.3.3                                        | 1 The evolution of multi-core processors                              | 62 |  |  |

|                | 4.3.2                                        | 2 Multicore technology at Intel                                       | 63 |  |  |

|                | 4.3.3                                        | 3 Multicore technology at Sun/Oracle                                  | 65 |  |  |

|                | 4.3.4                                        | 1 Tilera Corporation                                                  |    |  |  |

|   |     | 4.3.5      |       | NVIDIA CUDA architecture                             | 67    |

|---|-----|------------|-------|------------------------------------------------------|-------|

|   | 4.4 | 4          | Тахс  | pnomy of Parallel Computers                          | 69    |

|   | Re  | ferer      | nces  |                                                      | 70    |

| 5 |     | Mult       | i-thr | eaded programming                                    | 72    |

|   | 5.1 | 1          | Fund  | damentals of concurrent programming                  | 73    |

|   |     | 5.1.1      |       | Process Switching                                    | 73    |

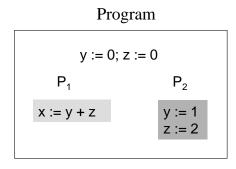

|   |     | 5.1.2      |       | Atomic actions                                       | 77    |

|   |     | Fine-grain |       | n atomic actions                                     | 77    |

|   |     | 5.1.3      |       | Composite atomic actions                             | 80    |

|   | 5.2 | 2          | The   | Critical Section                                     | 80    |

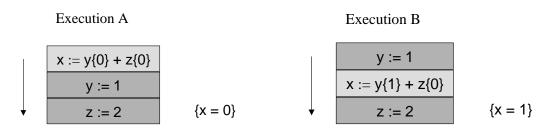

|   |     | 5.2.1      |       | The Critical Section Problem                         | 81    |

|   |     | 5.2.2      |       | Solving the Critical Section Problem: first attempt  | 82    |

|   |     | 5.2.3      |       | Solving the Critical Section Problem: second attempt | 84    |

|   |     | 5.2.4      |       | Solving the Critical Section Problem: third attempt  | 86    |

|   | 5.3 | 3          | Corr  | ect Critical Section Solutions                       | 88    |

|   |     | 5.3.1      |       | The Tie Breaker Algorithm                            | 88    |

|   |     | 5.3.2      |       | Hardware Support                                     | 90    |

|   | 5.4 | 4          | Sem   | aphores                                              | 91    |

|   |     | 5.4.1      |       | Case Study: the Dining Philosophers                  | 93    |

|   |     | 5.4.2      |       | Case Study: the Producer-Consumer problem            | 96    |

|   | 5.5 | 5          | The   | Monitor                                              | 99    |

|   | 5.6 | 5          | Mult  | tithreaded programming in Java                       | . 102 |

|   |     | 5.6.1      |       | The Java thread model                                | . 103 |

|   |     | 5.6.2      |       | Creating threads                                     | . 103 |

|   |     | 5.6.3      |       | Stopping the execution of a thread                   | . 106 |

|   |     | 5.6.4      |       | Communication between threads                        | . 106 |

|   |     | 5.6.5      |       | Implementing Mutual Exclusion                        | . 106 |

|   |     | 5.6.6      |       | Using condition synchronisation                      | . 107 |

|   |     | 5.6.7      |       | Example: The Producer-Consumer problem in Java       | . 108 |

|   |     | 5.6.8      |       | Parallel example: matrix-vector multiplication       | . 112 |

|   | 5.7 | 7          | Ope   | nMP                                                  | . 115 |

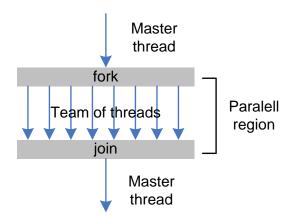

|   |     | 5.7.1      |       | Creating teams of threads                            | . 118 |

|   |     | 5.7.2      |       | Sharing work among threads                           | . 119 |

|   |     | 5.7.3      |       | Scheduling threads                                   | . 122 |

|                | 5.7.4   |         | Synchronization of threads                     |                    |

|----------------|---------|---------|------------------------------------------------|--------------------|

| 5.7.5          |         | 5       | Runtime library routines                       |                    |

|                | 5.7.6   |         | Parallel example: matrix-vector multiplication |                    |

| ļ              | 5.8     | Refe    | erences                                        |                    |

| 6              | Mes     | sage    | passing programming                            |                    |

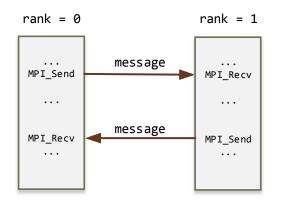

| (              | 6.1     | Me      | ssage Passing Models                           |                    |

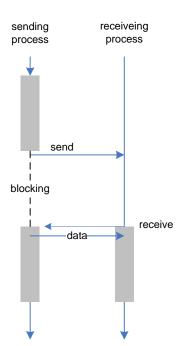

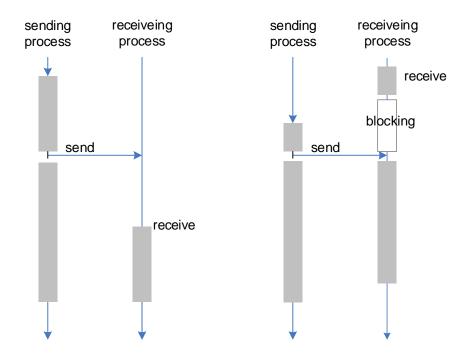

|                | 6.1.    | 1       | Synchronous message passing                    |                    |

|                | 6.1.    | 2       | Asynchronous message passing                   |                    |

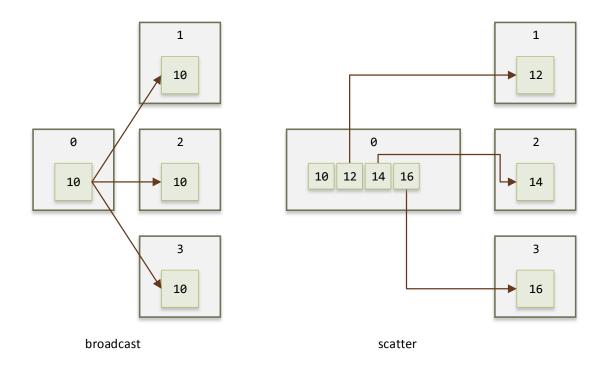

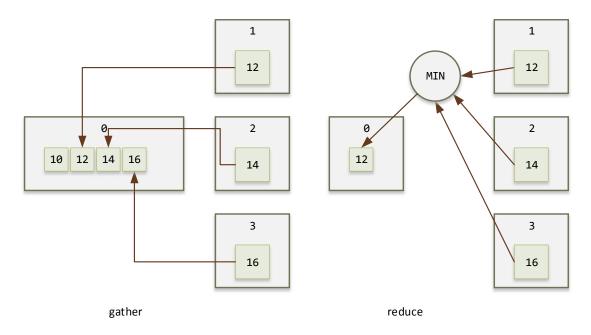

|                | 6.1.    | 3       | Collective communication operations            |                    |

|                | 6.1.    | 4       | Language support for message passing           |                    |

| (              | 6.2 M   |         | I – The Message Passing Interface              |                    |

|                | 6.2.1   |         | Basic MPI                                      |                    |

| 6.2.2<br>6.2.3 |         | 2       | Virtual topologies                             |                    |

|                |         | 3       | Collective communications                      |                    |

|                | 6.2.    | 4       | Non-blocking send/receive operations           |                    |

|                | 6.2.5   |         | Matrix-vector multiplication                   |                    |

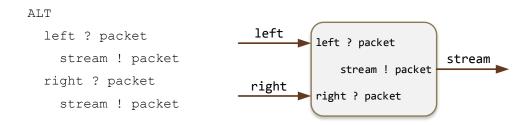

| (              | 6.3 Occ |         | am                                             |                    |

|                | 6.3.    | 1       | Introduction                                   |                    |

|                | 6.3.    | 2       | Language constructs                            |                    |

| 7              | Para    | allel A | Algorithms                                     |                    |

| -              | 7.1 Den |         | se matrix algorithms                           |                    |

|                | 7.1.1   |         | Data partitioning schemes                      |                    |

|                | 7.1.2   |         | Matrix transposition                           |                    |

|                | 7.1.    | 3       | Matrix-matrix multiplication                   |                    |

| -              | 7.2     | Solv    | ving systems of linear equations               |                    |

| -              | 7.3     | Solv    | ving partial differential equations            |                    |

| -              | 7.4     | Sort    | ting                                           |                    |

| -              | 7.5     | Gra     | ph algorithms Error! Boo                       | kmark not defined. |

# 2 INTRODUCTION

The fundamental reason for using parallel computing technology is to increase computing performance. There are always problems, applications that require more computational power that a single processor (processor core) can provide. Parallel computing is a practical answer to this problem, i.e., we want to solve the problem *now*. We cannot or do not want to wait for technological improvements (e.g. higher clock frequency) or new devices (optical or quantum computers); we need a solution in a practical timeframe. Thus, our only option is to use more of the readily available computing components.

But why exactly do we want ever increasing computing power? Why cannot we just stop and accept the currently available speed? What are the applications that require larger computational performance than what is currently available with sequential, single-processor/core machines. Here is a list of examples for such problems.

**Scientific calculations** – These include the traditional computational "Grand Challenge" applications, which are mainly simulations based on numerical calculations in the areas of physics, engineering, medical imaging, biological modelling, mathematics, weather prediction and so on. If, for instance, it takes 5 days to calculate the weather prediction for the next 2 days, there is not too much point in doing so. However, if we could decrease this time, say, to 10 hours, we could perhaps double or quadruple the accuracy of the prediction model.

**Multimedia systems** – The sheer amount of data in digitised images, video and sound files can be processed within reasonable time only with parallel computers. With sequential machines, even the simplest operation on a video sequence would take an unacceptably long time.

**Database systems** – Large databases create problems when large numbers of users try to perform complex queries. Search results can only be provided in reasonable time if several processors are working on different queries.

**Operating systems** – Current operating systems routinely run several tens of processes simultaneously. If these processes are spread onto several processors, instead of using only one, the performance and responsiveness of the computer will greatly increase.

**Services on the Internet** – Popular Internet applications and services (e.g. Google search, Amazon, Facebook, etc.) require server systems that can service millions of clients simultaneously in very little time. Parallel and distributed computing is the enabling technology for these systems.

For the past decades, the steady increase in the speed (clock frequency) of microprocessors guaranteed improved performance for the same program. Parallel computing was consequently a specialised area for those who wanted orders of magnitude larger computing power than available in the given or coming year. This has changed radically in the past few years. The absolute speed in the Universe is the speed of light. Even if we had working optical computers, we can never achieve execution speed greater than the speed of light. With currently available semiconductor technology, CMOS electronic components are used to build computers, consequently the speed limit is imposed by the propagation speed of electrons in silicon. Even if microprocessor manufacturers would achieve higher and higher operation speed in devices for many years to come, the speed of single-processor performance is bound by these physical limits. More fundamental engineering and manufacturing constraints, such as power consumption, heat dissipation, etc. brought an end to further increase in clock frequency. If we want more powerful computers in the future, we have two possible solutions.

- We invent and use fundamentally new computing technologies that can provide much greater computing speed and performance (e.g., optical, quantum or molecular computing).

- We try to use the existing technology in a more effective way, i.e. use several processors together and run parallel programs on them that are scalable to hundreds or thousands of cores.

Although there are encouraging experimental results with alternative computing technologies, currently the viable option is the second one, i.e. the use of more currently available processors. This can actually provide a very cost-effective way of creating powerful computers since the VLSI technology and the device speed do not necessarily have to be improved radically. The virtually unlimited increase in computing power hence is obtained by increasing the number of computing components in the system! This has been demonstrated in practice with the advent of multi-core processors and the many thousands of processors used in current supercomputers.

#### 2.1 PARALLEL COMPUTING HARDWARE AND SOFTWARE

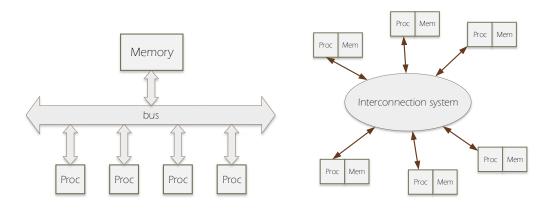

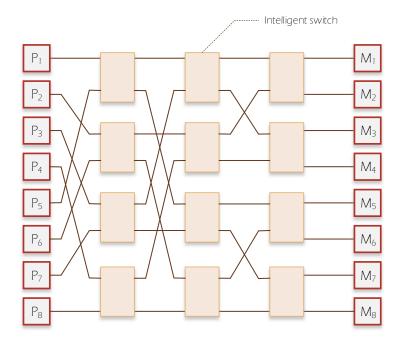

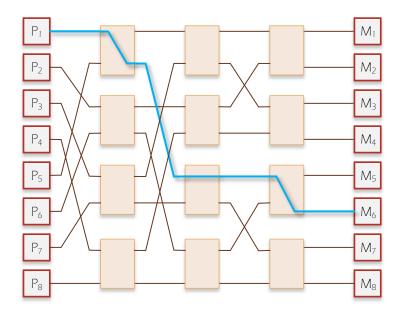

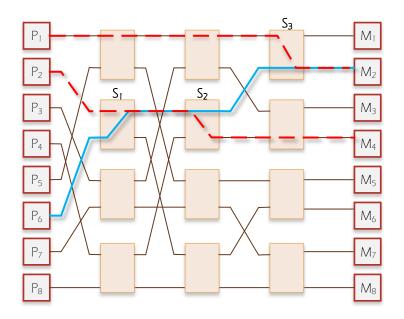

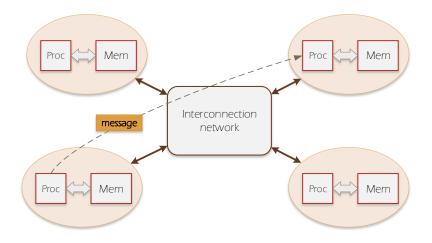

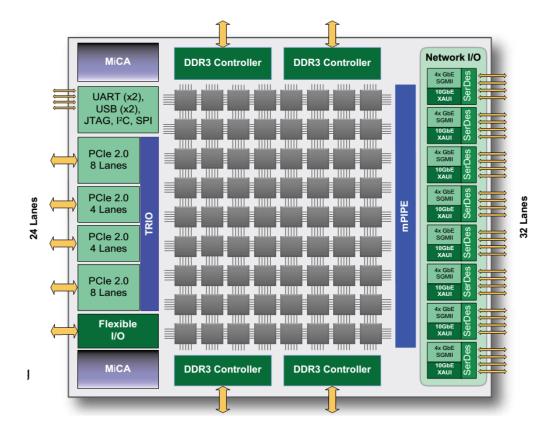

Just as for any sequential computing application, we need parallel hardware and software to create and execute a parallel program. The principal components of a parallel computer are a *set of processors*  $P_i$ , i = 1,...,p, one or more *memory blocks*, and an *interconnection system* that connects the processors and memory blocks together in an appropriate way. Depending on whether processors are connected to memory blocks or to other processors, we differentiate between shared memory and distributed memory parallel computers, accordingly. Figure 2-1 illustrates a typical shared memory and distributed memory parallel computer architecture. There are several variations of both types of architecture and especially of interconnection systems. Chapter 5 will describe these parallel architectures in detail.

Figure 2-1 structure of a typical shared-memory and distributed memory parallel computer. The word Proc stands for processors while Mem for memory modules.

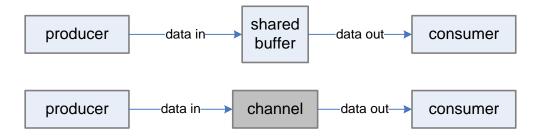

It is easy to see that if a problem is to be solved by a set of *processes* (program components executed in parallel), then processors will have to interact during the execution of the program. Most parallel programs require processes to exchange data. In shared memory computers, each processor can access the same global memory (address space), hence each can access variables that are used by others. As a consequence, processes running on shared-memory computers usually communicate through memory via shared variables. On the other hand, if memory is local to each processor, as in distributed-memory parallel computers, one processor cannot access data at a memory location of another processor. Therefore, they usually send messages to one other requesting or sending data from or to the given process. The underlying hardware architecture has profound effects on the choice of programming languages and on the performance of the applications, as we will see later in the book.

Once we have a parallel computer, we then need a parallel solution to the problem in question and a parallel programming language to express the solution in a way that is understandable for the machine. The aim of *parallel programming* is to express the solution of a problem in terms of smaller tasks and execute these subtasks in parallel to solve the original problem in shorter time. We are interested in firstly, how a given problem can be decomposed into a collection of parallel tasks and secondly, how we could express the parallel solution with a programming language. The first issue is about parallel program design, while the latter is on how to write a correct parallel program.

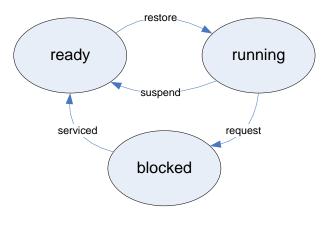

The key concept in a parallel program is the *process*. A process is a piece of sequential program code with its own data and state. A parallel program, hence, is a collection of processes. In parallel programs therefore, we must be able to manage processes (e.g., creating, stopping, etc—these features are not required in traditional sequential languages), and need language constructs that help in exchanging data among processes (communication) and synchronizing their actions.

The idea to divide a problem into smaller sub-problems, and then solve them in parallel at the same time sounds very simple, but unfortunately, as we will see throughout this book, things are much more complicated in practice. There are no clear-cut solutions as to how to create efficient parallel programs. But there are few general guidelines, approaches that can be used to help us in this task. The two main approaches to problem decomposition are based on partitioning either the input data set or the algorithm itself. Details of these methods are discussed in Chapter 3.

We have said earlier that there are two principal ways of exchanging data among processors: either by using shared memory variables or by message passing. To the analogy of the hardware models we will differentiate between programming languages based on *shared variables* and those using *explicit message passing*. Chapters 6 and 7 give an overview of the shared variable and message passing programming fundamentals along with the introduction of the most widely used parallel programming languages. Chapter 8 continues with examples of key parallel algorithms and examples of how they can implemented using different parallel languages and environments.

A parallel computing system that provides exceptional computing performance is almost a piece of art; a very complex masterpiece of engineering that is the result of careful combination of semiconductor, computer architecture, software engineering, algorithm and application design expertise. As it builds on so many types of knowledge, concepts of parallel computing should be present in computer science/engineering course and should not be taught in isolation.

This book intends to introduce the reader to the main areas of parallel computing technology. **Part 1** provides a general introduction to the parallel computing landscape and show the main paradigms that we can use to turn sequential problems parallel. **Part 2** concentrates on parallel computer architecture and examines the ways to construct parallel computers from processor and memory components. Both shared and distributed memory architectures are covered. **Part 3** focuses on parallel programming language issues. After an introduction to the problems of concurrency and parallelism in a program, it explains thread-based programming in Java, and describes the use of the OpenMP and Message Passing Interface standards. **Part 4** describes some of the most common parallel algorithms and provides implementation examples.

## 3.1 COMPUTATIONAL PERFORMANCE

Parallel computing is about computational performance. Without properly measuring the performance we cannot reason about our algorithms or compare different computers with one another. Since the main use of parallel computers is for numerical computations in the computational science community, the key metric of computing performance is the number of *floating-point* numerical *operations* the computer can perform in *a second*. From the abbreviation of this long term came the unit *flops* or *flop/s*. Since processors can execute a very large number of operations in a second, we normally measure them in larger units, such as Mflops (mega 10<sup>6</sup>), Gflops (giga 10<sup>9</sup>), Tflops (tera 10<sup>12</sup>), Pflops (peta 10<sup>15</sup>) and Eflops (exa 10<sup>18</sup>). In comparison, a typical desktop processor core has a performance typically in the range of 1-15 Gflops running at 100% CPU load.

#### 3.2 SUPERCOMPUTING AND PARALLEL COMPUTING

Since the invention of digital computers, engineers were engaged to design and build a faster computer than the existing ones. The fastest computers in the world are historically called *supercomputers*. Computing on these computers is called *supercomputing* and the companies making these computers and the associated software packages together form the *supercomputing industry*. Supercomputing really started in the 1960s, when solid state semiconductors allowed sufficient size reduction of the required components. Seymour Cray founded Cray Research who created the Cray-1 (1976), shown in Figure 3-1, that achieved approximately 80-130 Mflops performance [1]. Several new models followed, like the Cray-2 (1985, 300 Mflops), the Cray X-MP and Cray Y-MP (1988, up to 15 Gflops), dominating the supercomputer industry till the 1990's. The cost of these computers was in the range of million US dollars. The most important thing to note is that from the Cray-2 model onwards these computers used multiple processors to achieve supercomputer performance. Parallel computing and supercomputing technology development hence went hand-in-hand.

In the 1990s, the number and the speed of processors increased higher and higher and soon, supercomputers achieved the 100 Gflops performance range. Japanese and US manufacturers competed for the fastest computer title. Notable supercomputers from this era are the Fujitsu

Numerical Wind Tunnel (1994, 166 processors, 124 Gflops), the Hitachi SR2201 (1996, 2048 processors, 600 Gflops), the Intel Paragon (1994, 3680 processors, 143 Gflops) and the Connection Machine CM-2 (1987, 65 536 1-bit processors, 6 Gflops) and CM-5 (1993, 1024 processors, 131 Gflops).

Figure 3-1 The Cray-1 computer (Cray Research) [2]

Figure 3-2 Connection Machine 2 (Thinking Machine Corp.)<sup>1</sup>

Figure 3-3 ASCI Red, the first teraflops computer<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> Image source: http://www3.sympatico.ca/n.rieck/images/TM-CM2-0109-SUPERCOMP\_x600.jpg

<sup>&</sup>lt;sup>2</sup> Image source: http://www.computermuseum.li/Testpage/ASCII-RED-Supercomputer.gif

Having created many computers in the hundred Gflops range, the supercomputing industry was after its next challenge: to achieve teraflop computing performance. This was achieved by the US research and development program ASCI (Accelerated Strategic Computing Initiative) [3] whose aim was – among others – to build several teraflops supercomputer from commercial, off-the-shelf components. This decision started an important development path that resulted in computers that could be more easily upgraded and supported the porting of parallel software packages better. The result of this effort was unquestionable since the first computer breaking the Tflops barrier in 1997 was the ASCI Red supercomputer (2.4 Tflops). Not long after a successful series of Tflops-range ASCI computers (ASCI Red, White and Blue), Japan created the Earth Simulator supercomputer that achieved 32 Tflops performance and became the first teraflops computer built outside the US.

By 2008, the supercomputing industry reached the petaflop performance range. The IBM RoadRunner computer was the first to break the petaflop barrier achieving 1.026 Pflops sustained performance in 2008. Development has not stopped since, and at the end of 2013, the world's fastest computer – the Chinese Tianhe-2 – works at over 33 petaflops speed (shown in Figure 3-5).

Figure 3-4 The first petaflops supercomputer – RoadRunner, IBM Blue Gene/P<sup>3</sup>

<sup>&</sup>lt;sup>3</sup> Image source: http://upload.wikimedia.org/wikipedia/commons/d/d3/IBM\_Blue\_Gene\_P\_supercomputer.jpg

The development of the most powerful supercomputers in the world can be followed by studying the TOP500 list that measures the performance of the most powerful computers twice each year (http://www.top500.org). Very interesting trends and developments can be discovered from the data sets of this archive. At the time of writing, the five most powerful supercomputers in the world are the followings. The readers are advised to consult the TOP500 list for further details.

| Rank | Name/model         | Country | Number of<br>cores | Performance<br>[petaflops] | Power<br>consumption<br>[megawatt] |

|------|--------------------|---------|--------------------|----------------------------|------------------------------------|

| 1    | Tianhe-2           | China   | 3 120 000          | 33.8                       | 17.8                               |

| 2    | Titan - Cray XK7   | USA     | 560 640            | 17.6                       | 8.2                                |

| 3    | Sequoia BlueGene/Q | USA     | 1 572 864          | 17.1                       | 7.9                                |

| 4    | K Computer         | Japan   | 705 024            | 11.3                       | 12.6                               |

| 5    | Mira BlueGene/Q    | USA     | 786 432            | 8.6                        | 3.9                                |

| Table 3-1 | The top five supercomputer in the world (as of November 2013). |

|-----------|----------------------------------------------------------------|

|-----------|----------------------------------------------------------------|

Figure 3-5 Tianhe-2 supercomputer, China<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> Image source: http://www.engineering.com/Portals/0/BlogFiles/DesignerEdge/1113/Tianhe-2.jpg

#### **3.3** PARALLEL COMPUTERS FOR THE MASSES

Needless to say, these supercomputers are very expensive, their cost can reach 100 million USD per system and use megawatts of energy. Very few countries in the world can afford the installation and operation of such giants. If parallel computing was only about supercomputers, not many of us could ever run a parallel program. Fortunately, there are more economical alternatives that - for an individual user - may provide just as good performance. Network connected desktop computers, also known as computing clusters, can easily achieve teraflops range performance at no additional cost. This form of computing is especially popular at universities where existing laboratory computers can be efficiently utilised for solving computationally intensive problems. Assuming 4-core computers, a lab with 50 computers (200 cores) can achieve around 2 teraflops performance. Another alternative is to use graphics cards either as single units or as components in clusters. Top graphics card today can achieve 3-4 teraflops computing performance at a fraction of the cost of a PC. Using about 30 such cards together, one can achieve over 100 teraflops. For students entering the world of parallel computations, common dual or quad-core notebook computers are perfectly adequate to explore techniques and study parallel algorithms and program development.

Figure 3-6 Xeon Phi, Intel's 60-core, 1Tflops HPC coprocessor [4]

Figure 3-7 NVIDA Tesla K40 GPU accelerator, 2880 cores, 4.29 Tflops [5]

#### **3.4** SOLVING PROBLEMS IN PARALLEL

Having looked at parallel computers of different sizes, one starts to wonder whether there is a method that we can follow to make an existing sequential program suitable to run on a multiprocessor computer. Is there perhaps some 'magic' that can transform a program into a parallel form? The answer is that automatic parallelisation of a sequential program only works on special problems and in limited situations. Normally, the programmer has to design the parallel structure and operation of the program. Unfortunately, there is no universal recipe for creating parallel programs, or in other words, parallelising sequential programs. There are tools that can help but, in the end, it is the program designer who must make the key design decisions.

Students are normally trained to solve computer programming problems in a sequential fashion. We are taught that a computer executes instructions one after the other in strict sequential order. If we want to change the order, we use branching instructions. These fundamental concepts – sequence, branching and loops – are also used in parallel programs but we need to liberate ourselves by allowing several tasks to proceed at the same time. If we think of analogies, we will discover soon that life around us is in fact parallel; e.g., we hardly ever build a house or manufacture a product using one single worker. To save time, we would use many workers, often having different skills, in a coordinated way. A good work manager is also needed who ensures that workers will have access to resources and can perform their tasks in the most optimal way.

At the very highest level, our problem is reduced to finding work units that can be assigned to processors, ideally without any dependency from others. The art of parallel computing is to discover the most efficient way of splitting a solution to smaller sub-problems and make it suitable for the target computer that can execute it with maximum efficiency. We will see later in this book that creating parallel programs is not always trivial. It requires time and energy to develop an efficient parallel program. One has to be careful in judging whether or not a parallel implementation is beneficial. For instance, there is little use of spending weeks on parallelising a program that will only be run once and the execution time of the program is, say, few minutes. We are better off waiting few minutes instead of working for weeks. Remember that parallel computing is about speed. If the outcome of our effort cannot justify the parallel programming effort, do not do it. If, however, the potential benefits are great indeed, try to find every trick to make the program run as fast as possible!

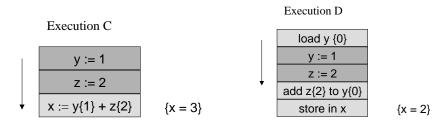

The starting point for solving any problem in parallel is to find sub-problems that can be executed by different processors at the same time. This method is called *partitioning*. By finding smaller and smaller tasks, we potentially increase the level of parallelism in the solution. Depending on how many sub-problems we end up with, we differentiate among *low*, *medium* and *high-granularity* parallelism. An algorithm has low granularity if the tasks are built up from many larger functions. A medium granularity problem can have tasks executing instructions at the function level. In high-granularity parallel programs tasks are instruction level entities.

Besides partitioning, another key concept in parallel computing is *efficiency*. It is no use to have many parallel tasks if they cannot run on the system efficiently. If tasks are delayed for any reason, the time wasted – also known as overheads – will reduce the overall performance of the system. In the worst case, tasks can even execute sequentially if resource or other dependencies dictate that way. Overheads can arise from communication delays, synchronisation with other tasks, not having enough computing resources or work to execute. We will investigate these issues later in more detail. In the rest of this section, we will look at the most common forms of parallelism that we can effectively use in our parallel programs. Remember, there are no 'recipes' to perfect and automatic parallelisation, each problem requires a fresh look, but based on experience gathered over the past two decades, we can identify distinct approaches to or 'styles' of parallel executions. These are based on *what* we make in the program parallel and *how* the parallel processes are then executed.

#### 3.4.1 Data or geometric parallelism

There are many problems where the solution requires repetitive computations on varying data. Typical examples are transformations of one, two or three-dimensional matrices, processing pixels in images, simulating physical properties of objects. The core of the computation is the same for each data items, hence normally a loop is used to iterate over the data set. A very simple example is the calculation of the square of the first *N* natural numbers. The sequential code would be the following:

```

for (int i=1; i<=N; i++)

{

result[i] = i * i;

}</pre>

```

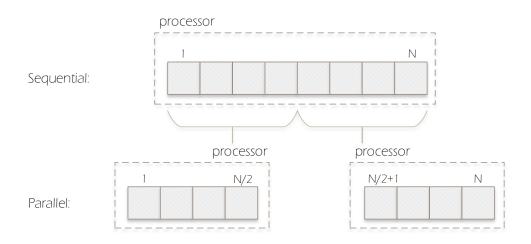

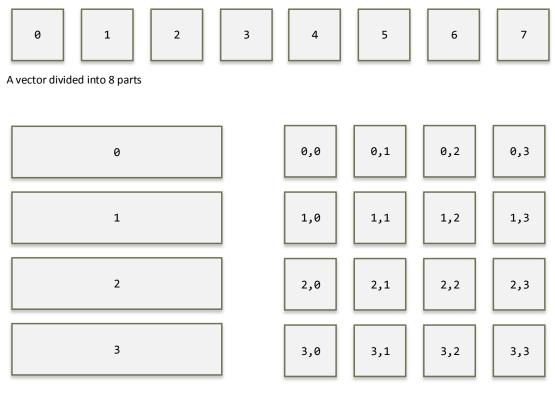

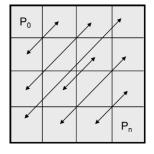

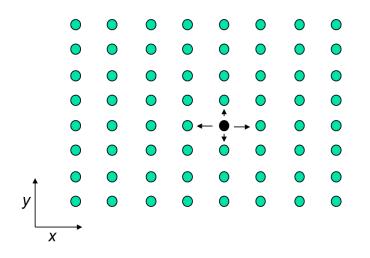

A single core will finish the operation in *N* steps. If each step takes *T* time to complete, the entire operation will execute in *N*·*T* time. If we visualise the data set, we see a one-dimensional array, a vector that the program fills up with the value  $i^2$ , where i = 1...N. Notice that the iterations of the loop do not depend on each other, i.e. the calculation of each iteration can be done independently of the others. Let us divide now this set into *k* non-overlapping equal parts, where p = 2...N, and we end up with parts having *N*/*p* items. Now, we assign each part to a processor and assume they execute the same code on the smaller data sets at the same time. Figure 3-8 illustrates this process for the p = 2 case, i.e. using 2 processors.

The original loop will be split into two loops, one for each process. Process 1 will execute the loop for the first N/2 items, Process 2 will perform the second N/2 items. The code for the two processes will be as follows.

```

Process 1: Process 2:

for (int i=1; i<=N/2; i++)

{

result[i] = i * i;

}

Process 2:

for (int i=N/2+1; i<=N; i++)

{

result[i] = i * i;

}

</pre>

```

In the ideal case, the program will finish in half of the original execution time. As we increase the value of p, more and more processors are used and the execution time is reduced. Using N processors, the program will finish in 1 time unit.

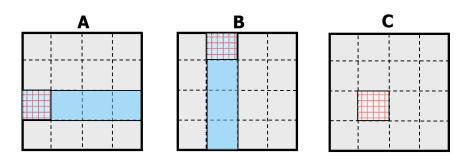

Figure 3-8 Partitioning a data set for data-parallel execution.

The same concept can be used for higher-dimensional data structures. As an aside, we note that the granularity varies with the data size – processor number ratio. For a given data size N, if we have 2 processors, on the other hand, if the number of processors are close to the data size, the granularity is high, the processors will work on very few data items.

Let us continue with two examples of a two-dimensional and three-dimensional computational problem.

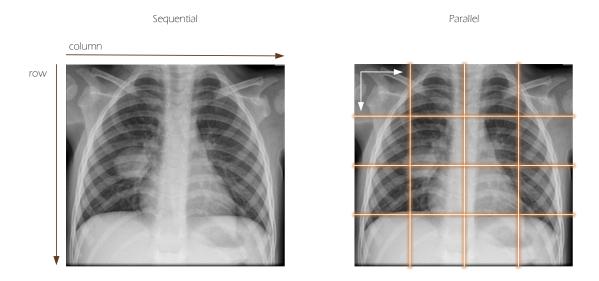

#### Image processing

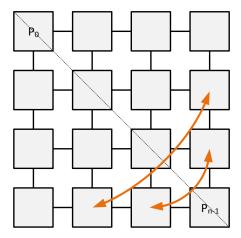

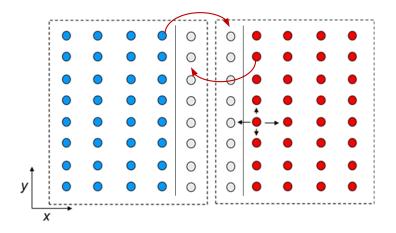

Imaging application have to manipulate pixels in large digital images. Even a simplest operation, for example, increasing the intensity or contrast, require lengthy computations as each pixel must be processed in the image. Figure 3-9 illustrates the sequential and parallel approach to this typical processing strategy. In the sequential case, the image is represented as matrix with N rows and columns (for simplicity, we assume square images). A double nested **for** loop is used to visit each pixel and apply the required operator. With today's technology, the number of pixels in the images range from 10<sup>6</sup> (mega) to 10<sup>9</sup> (giga) pixels.

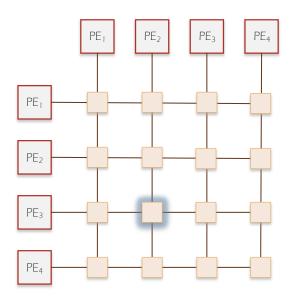

Since the pixel operations are independent form each other, they can be executed in a dataparallel fashion. One possible positioning of the image data is shown in Figure 3-9. The image is split into smaller square tiles of size  $M \times M$ , where  $M = N / \sqrt{p}$  and p is the number of processors. Using 16 processors, as in the example, each processor will work on an  $N / 4 \times N / 4$  sub-image and the execution time of the entire operation is reduced to the  $1/16^{\text{th}}$ of the original.

Data parallelism is a very natural way of dividing a large computational problem into simultaneously executable parts. The main advantage of this approach is that the parallel program can be easily adjusted to the number of available processors. If there is no data dependency among the parallel tasks, near ideal performance can be achieved. Luckily, a very large part of the computational problems (especially scientific – numerical – calculations) fall into the data parallel category.

Figure 3-9 Data-parallel partitioning of an X-ray photograph for pixel manipulation.

# 3.4.2 Control or algorithmic parallelism

There are problems whose solution requires complex computational steps and the execution time is determined by the operations, not the size of the data. In fact, in many cases, the data set is constant or small. Our only hope to speed up such programs is to execute different instruction sequences (partial calculations) in parallel. This method is called control or algorithmic parallelism. Ideally, our problem can be divided into partially or fully independent sequences of statements (tasks).

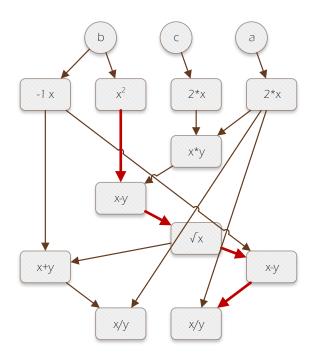

We illustrate the algorithmic parallelism in a simple example. Assume that we need to compute the roots of a quadratic equation. For the sake of simplicity, we assume that execution time of the floating point operations is so great that we must create a parallel implementation for the calculation. The roots are given by the well-known equation:

$$x_{1,2} = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a}$$

A sequential program would take the three input parameters a, b, and c, and evaluate the terms of the above equation in succession. The calculation of each root will require 9 floating point operations – assuming that the square root is one operation.

The input data set is always the three parameters, and the calculation is not repeated for a, b, and c, as in the data-parallel case. We need to find parallelism in the evaluation of the

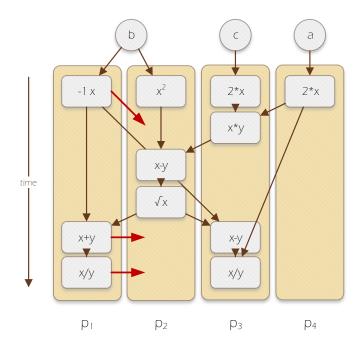

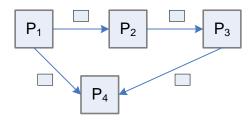

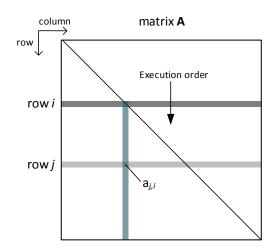

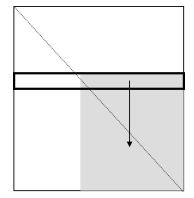

expression. Figure 3-10 depicts the execution graph of computing the root. The input variables are represented by circles, and the different floating point operations are shown in rounded rectangles. Each rectangle transforms the data it receives at the top and sends it forward at the bottom. If two inputs are given, the operation is executed from left to right inputs, i.e. left input = x, right input = y. This representation is also known as the dataflow graph as it clearly shows how data flows through the computing network as it is transformed. The result is produced at the last nodes of the graph at the bottom.

*Figure 3-10 Execution graph of the quadratic equation root calculation. The red arrows indicate one critical path of the execution.*

The question now is whether or not the different operations can be executed in parallel and if so, what is the level of parallelism in the system. The graph shows dependencies (on is highlighted in red) that must be executed serially, one after the other but also displays opportunities for parallel execution. By slightly rearranging the graph, we can create a so-called space-time diagram (Figure 3-11), commonly used in parallel computing which displays how the tasks are executed by each processor and in which order. Since the maximum number of independent processes are 4, the graph is mapped onto 4 processors. The diagram also indicates the time required for the execution of the calculation. Assuming that each operation takes 1 time unit, adding the rows from top to bottom produces the overall parallel execution time. In this case, 6 units. Since the original serial calculation required 9 operation, we are less

than optimal. With four processors, we would like to see an execution time of 9/4 steps. We can see, that the use of the processors is less than optimal. None of the processors are busy constantly; processor  $p_4$ , for instance only performs one operation. By merging the tasks of processors  $p_1$  and  $p_2$ , we can reduce the number of processor to 3 without increasing the execution time. While this step did not reduce execution time, it definitely made the overall system more efficient.

Even this simple example can show that the amount of parallelism in algorithmic parallelism is limited. It is hard to find problems and parallel solutions in which a large number of processes can execute in parallel. Moreover, it is quite difficult to find the independent parts in an execution graph, and partitioning an algorithm into *k* tasks does not mean we can execute all *k* tasks at the same time. There might be data dependencies that will require sequential execution of certain tasks! If we want large increase in computing power, we normally try to use the data parallel paradigm.

Figure 3-11 Space-time diagram of the execution of the graph in Figure 3-10. Red arrows indicate how tasks of  $p_1$  can be moved onto  $p_2$  without increasing execution time.

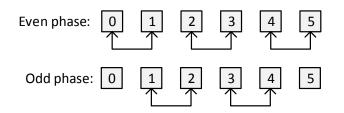

#### 3.4.2.1 Pipelining

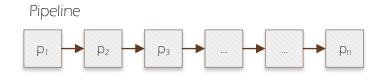

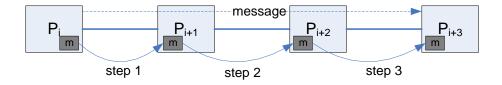

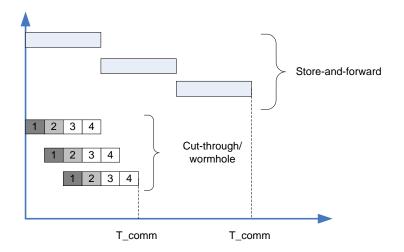

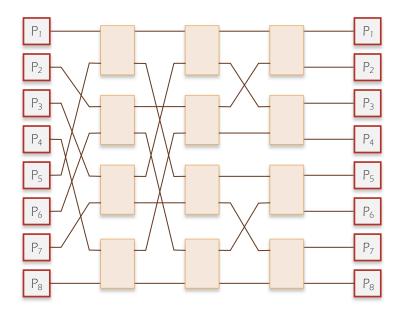

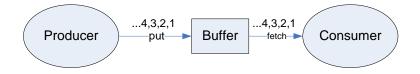

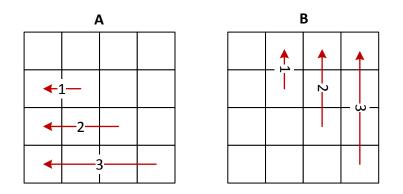

Pipelining is a special form of control parallelism - the output (the result) of one process becomes the input of the next one. The idea of pipelining is not new, it has been widely used in sequential processors and in vector supercomputers. Although the pipeline structure (shown in Figure 3-12) resembles sequential execution, it is in fact an efficient parallelisation strategy when data must be processed in successive stages to produce the final result.

Figure 3-12 Processing in a pipeline. Each process sends its output to the next one which will use it as an input data to work on.

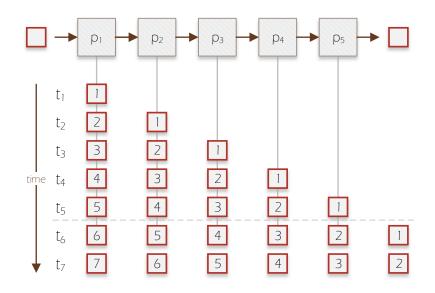

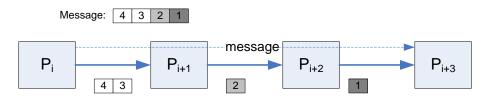

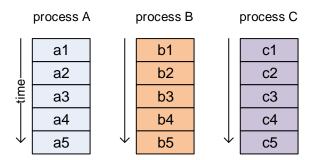

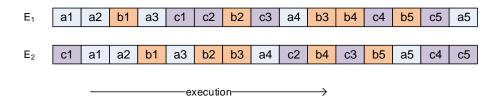

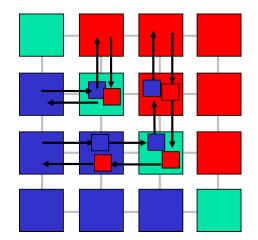

To understand how the pipeline can reduce execution time, let us look at the operation example shown in Figure 3-13. We assume that our data takes 5 sequential stages to be processed. These stages are assigned to processors in a five-processor pipeline. Data is then pushed into the pipeline at processor  $p_1$  which will perform the calculation steps of the first stage of the processing steps then pass the result on to processor  $p_2$ . Processor  $p_2$  then will do its share of the calculation and pass the result on to  $p_3$  and each consecutive processor will work similarly. As we can see in Figure 3-13, in each time step, a work package travels to the next stage of the computation. See, how work package 1 travels from the start of the pipeline to the end in 5 time steps. When we start the calculation, the first work package is in processor  $p_1$ . All other processors are *idle*. When  $p_2$  starts its computation,  $p_1$  is already working on the second work package. At each time step one more processor becomes active in the pipeline.

Once the first package reaches the last stage of the pipeline, in this case  $p_5$ , the pipeline is said to be *filled*. From this moment, the pipeline will produce one result in every time step (see  $t_6$ and  $t_7$ ), even though the entire processing time for the input data takes 5 time steps. Therefore, the execution time is reduced from 5 to 1 units which is a factor of 5 performance gain over the sequential execution. More formally, in situations when the time of filling the pipeline is negligible to the overall execution time, the execution time becomes  $T = T_{sequential} / P$ , where P is the length of the pipeline. This explains how the pipeline can speed up calculations of transformation sequences, and show that the longer the pipeline becomes, the more we can reduce the execution time.

*Figure 3-13* The flow of work units in a pipeline.

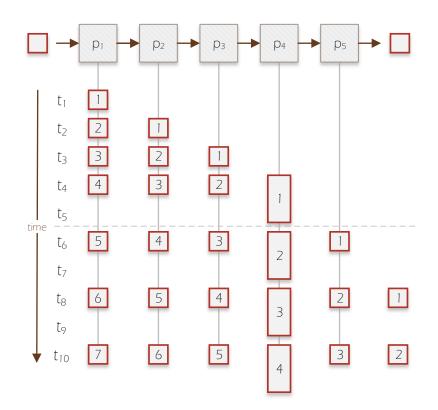

The above example used an idealised scenario in which each stage takes an equal amount of time to complete. This type of pipeline is called a *balanced* pipeline. Let us examine what happens if different stages of calculations take different amount of time in the pipeline. This is illustrated in Figure 3-14, where the execution time of processor  $p_4$  is twice the time of the others. We can see that from the moment  $p_4$  starts working, the execution time of each stage is determined by the execution time on  $p_4$ . This is because the processors work in a lock-step fashion. No matter how fast one processor completes its work, it will not be able to send or receive its next work package while  $p_4$  is busy, hence, eventually  $p_4$  will control the execution. Consequently the speedup in a general pipeline is given as the ratio of the sequential execution time (total work unit execution time) to the pipelined execution time (time of producing one result with a full pipeline):

$$S = \frac{\sum_{i=1}^{N} T_{p_i}}{\max_{1 \le i \le N} T_{p_i}}$$

This shows the weakness of pipelines: in order to gain large performance increase we need long pipelines and nearly identical processing times for each stage (processor). It is very difficult to find problems where the pipeline can be long p > 10 and also very hard to ensure that all processes will have equal execution times.

#### 3.4.3 Farming parallelism

In our discussion so far, we were looking at how to split the data or the algorithm of a problem into smaller parts. We implicitly assumed that the execution time was known before we partitioned the problem and the time of each subtask is always constant.

There are many examples for which this assumption is not valid. Either we do not know the execution time when we split the problems, or the time depends on runtime parameters, i.e., the computational cost of the subtasks changes dynamically. In these cases, both data and algorithmic-parallel programs can result in an inefficient use of the processors if some processors receive more work than the others; the less loaded processors will spend time waiting for others instead of doing useful computation. This is known as the computational *load imbalance* problem, which we will later discuss in more detail.

Farming parallelism, also known as Master/Slave or Master/Worker parallelism is a dynamic work allocation strategy that ensures that processors are uniformly loaded with work even in a dynamic environment. This strategy can be used equally well for data or control-parallel

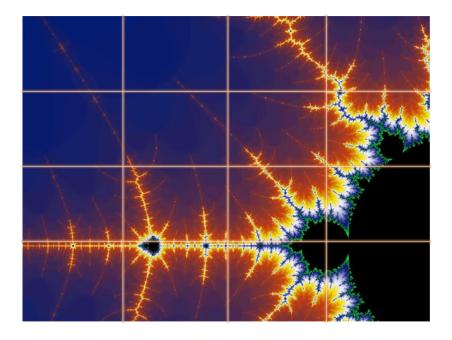

programs. We illustrate the operation of the farming parallelism strategy with a well-known computational problem, the calculation of the Mandelbrot Set. Figure 3-15 shows the visual representation of the Mandelbrot Set. This is a famous example of fractal geometry invented by Benoit Mandelbrot. The picture shows the results of the membership function of the following recursive function on the complex plain:

$$z_n = z_{n-1}^2 + c$$

where n = 0, ..., N, c is a complex number in the plane to be tested for membership and  $z_0 = 0$ . A point c is in the set only if  $|z_n| \le 2$  for all  $n \ge 0$ . The point of each point c is relative to the value of n where the condition  $|z_n| \le 2$  fails. Points that are in the set are coloured black.

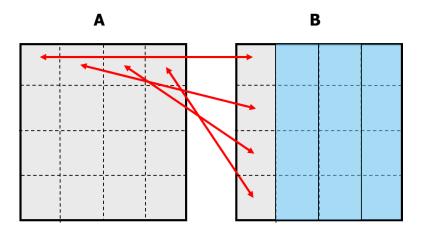

Since the same program (membership test) part is executed for each point (pixel) of the plane, this is a potential data-parallel problem and could be divided into subparts as shown in Figure 3-15 (p = 16). The trouble with this approach is that the rectangular areas assigned to each processor will take varying time to execute and even worse, we do not know who long each part will run. This is because the membership test includes a conditional expression that can only be evaluated at runtime.

Figure 3-15 Visual representation of the Mandelbrot Set along with one possible work partitioning for 16 processors.

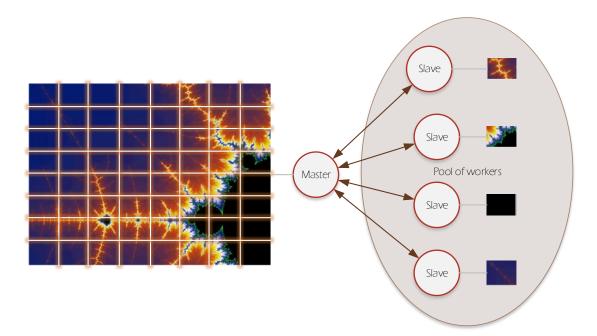

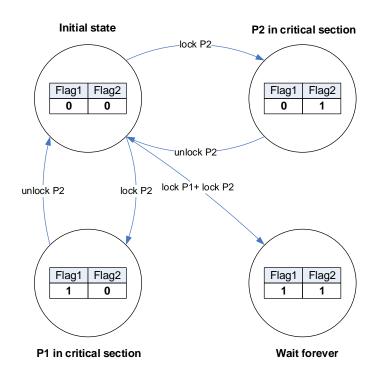

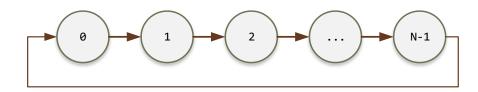

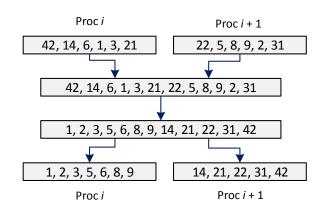

The farming parallelism approach uses a master controller acting as a work dispatcher to 'farm out' tasks to worker or slave processors. The operation is simple. Slaves only perform work. When a slave finished with the work, it returns the result to the master which, in turn, 27 dispatches the next task to the slave. This cyclic pattern is repeated until all tasks are completed.

It is easy to see that if we use the exact same 16 work units and p = 16 processors as in Figure 3-16, the situation would remain the same. Each processor would execute for some (unknown) amount of time and when the last one finished, the image is complete. The central idea in farming parallelism is that the problem is divided in such a way that the number of computational units (work packages) is much larger than the number of processors. The many small work units statistically even out imbalance of the processors; those receiving tasks taking longer to compute will execute fewer tasks, the ones with short tasks will execute more. It has been shown that with this approach it is possible to keep processors busy and achieve good load balance and high performance.

Figure 3-16 Using the farming parallelism approach for the Mandelbrot Set calculation problem.

#### 3.5 PARALLEL EXECUTION PERFORMANCE – THE BASICS

In this section we look at the most fundamental metrics that can help measure the performance of a parallel system and the level of success in creating an efficient parallel program. We discussed ways of partitioning a problem into subtasks for parallel execution but we need objective metrics that inform us about the performance of the solution.

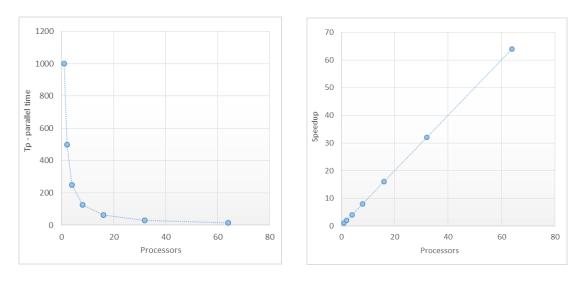

The execution time  $T_s$  of the sequential program we will parallelise will serve as a baseline to which we will compare the parallel system. Let  $T_p$  denote the execution time of the parallel program. Ideally, the parallel time is the sequential time divided by the number of processors, p, thus

$$T_p = \frac{T_s}{p},$$

which is the inverse (or reciprocal) function of p, so by doubling the number of processors (p = 1,2,4,8...64,...), the execution time will be halved as shown in Figure 3-17. When measured, however, we often get a sub-optimal value.

We define the ratio of the sequential to the parallel execution time as the *speedup* of the parallel system. The speedup,  $S_p$ , is a metric that indicates the execution speed gain of the parallel program over the sequential one and is defined formally as

$$S_p = \frac{T_s}{T_p}.$$

By substituting the ideal parallel time,  $T_p = T_s/p$ , into the speedup formula we see that in the ideal case

$$S_p = \frac{T_s}{\frac{T_s}{p}} = p,$$

that is, a speedup is equal to the number of processors. The graphical representation of the ideal speedup is shown in Figure 3-18. Theoretically, speedup should be derived using the sequential time  $T_s$  measured on the fastest processor running the most efficient sequential algorithm; this is the *absolute speedup*, showing how much faster our program is when compared to the fastest possible sequential execution. In practice, obtaining this best sequential execution time is almost impossible. For this reason, we typically use a more relaxed form of the speedup which is called the *relative speedup*, which is derived from the execution time of the sequential algorithm forming the basis of the parallel implementation on one processor of the parallel computer. This relaxed sequential execution time is denoted by  $T_1$ , and the relative speedup is defined as

$$S_p = \frac{T_1}{T_p},$$

where  $T_p$  is now meant as  $T_p = T_1/p$ .

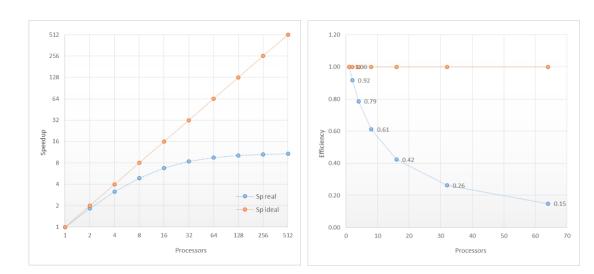

Figure 3-17 Parallel execution time

Our last metric is *efficiency*, *E*, which describes how efficiently the parallel system achieves the measured speedup. Efficiency is defined as the ratio of speedup to the number of processors used in the system,

$$E=\frac{S_p}{p}.$$

Clearly, a speedup of 12 achieved on a 12-processor system is a far more efficient execution than the same achieved on a 64-processor one. From the definition of speedup we can see that the ideal efficiency is E = 1, that is, 100%.

#### 3.5.1 Suboptimal performance

In real applications, achieving ideal performance is nearly impossible. There are various overheads owing to hardware, algorithm and execution properties that result in wasted time during execution (e.g. copying data to processors, sending work packages in a farming parallel program, synchronising processes). The total overheads have an important effect on performance.

Gene Amdahl was among the first researchers to warn against over optimism in parallel computing. In his paper [6] he states – what is now known as *Amdahl's Law* – that there will always be a portion of the program that cannot be made parallel and therefore will put a limit to the achievable speedup. Let  $\alpha$  denote the part of the program that cannot be parallelised. Then, the parallel execution time can be expressed as follows:

$$T_p = \alpha T_1 + \frac{(1-\alpha)T_1}{p}$$

The first term of the expression is the time of the remaining sequential part while the second term is the ideal execution time of the fully parallel part. When we express the speedup using this expression and take its limit we get

$$\lim_{p \to \infty} S_p = \frac{T_1}{\alpha T_1 + \frac{(1 - \alpha)T_1}{p}} = \frac{p}{\alpha p + (1 - \alpha)}$$

$$= \frac{p}{1 + (p - 1)\alpha} = \frac{1}{\frac{1}{p} + \left(1 - \frac{1}{p}\right)\alpha} = \frac{1}{\alpha}$$

This limit effectively means that the speedup is bound and is independent of the number of processors. Put it simply, if 10% of the program cannot be made parallel, the maximum speedup we can achieve is  $S_p = 10$  regardless the number of processors used!

This somewhat contradicts the fact that supercomputers are built with hundred thousands of processors. Surely, people would not spend millions of dollars without good reason. While Amdahl's Law is certainly valid in general, as John Gustafson pointed out [7], for most engineering and scientific problems, the sequential portion  $\alpha$  becomes a function of the problem size n, that is,  $\alpha(n)$ , which normally becomes smaller as n increases:

$$\lim_{n\to\infty}\alpha(n)=0$$

Taking the limit of the speedup using  $\alpha(n)$  in terms of problem size n results in

$$\lim_{n \to \infty} S_p = \frac{p}{1 + (p-1)\alpha(n)} = p$$

showing that ideal speedup in fact can be achieved given that the sequential portion approaches zero for large problem sizes. This is also known as *Gustafson's Law*.

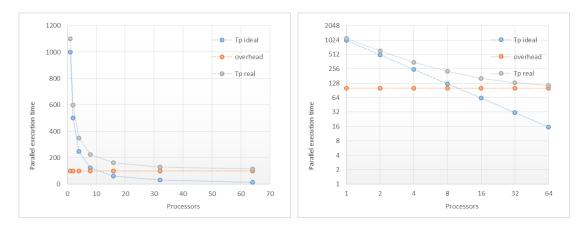

Before moving forward, let us look at the visual representation of the performance metrics we have discussed above taking the overhead into consideration.

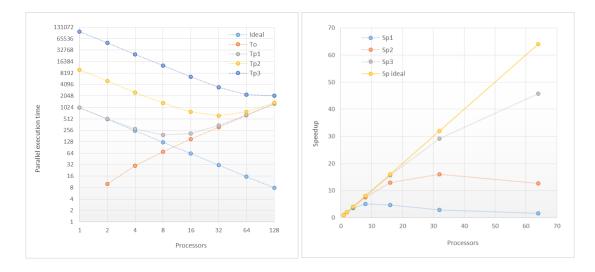

Figure 3-19 shows the ideal parallel execution time  $T_p^{ideal}$  as a function of p for  $p = \{2,4,8,16,32,64\}$ . Notice that doubling the number of processors halves the execution time. Also shown, the realistic parallel execution time including overhead (e.g. sequential portion of the program). The constant overhead is also displayed separately. As expected, the execution time converges to the overhead value. For large number of processors and small overhead, the ideal and realistic execution time curves are very difficult to distinguish, as the reciprocal *x* function is the smallest for large *x* values, where we are most interested in the results. For this reason, an alternative plot, shown in Figure 3-20, should be used for the execution time where each axes uses a log scale (preferably base 2). This transforms the execution time to a straight line in the ideal case and a curvy one for the realistic cases. The log scale amplifies the small changes at large processor values and makes it visually trivial to spot non-ideal performance (is it a straight line or not?).

Figure 3-19 Parallel execution time

Figure 3-20 Parallel execution time shown in log-log scale

Figure 3-21 Ideal vs. realistic speedup curves.

*Figure 3-22 Ideal vs. realistic efficiency curves.*

Unfortunately, parallel computing in practice is more complicated that we could describe the performance with asymptotic limit analysis. In parallel programs running on multi-processor computers, there are various overheads present that are due to hardware, software and algorithmic factors, for example time lost due to:

- communication and synchronisation among processes,

- waiting for shared resources,

- processors not having enough work to do, or

- not having enough parallelism in the problem.

We can represent the various overhead effects (some being constant, or a function of p or problem size n) as an overhead function  $T_o(p, n)$ . The use of this overhead function allows us to investigate the performance of our parallel system not only for unrealistically large number of processors but for practical system sizes too. This is crucial as the shape of the overhead function has enormous effects on performance, as we will see below.

Let the parallel execution time include the overhead term as

$$T_p(p,n) = \frac{T_1}{p} + T_o(p,n)$$

The parallel time and the speedup now becomes functions of p and n as well.

Overheads

$$S_p = \frac{T_1}{\frac{T_1}{p} + T_o(p,n)} = \frac{T_1}{\frac{T_1 + pT_o(p,n)}{p}} = \frac{T_1 p}{T_1 + pT_o(p,n)}$$

If we assume  $T_o$  is constant, taking the limit of the speedup results in Amdahl's Law if  $T_o$  represents the sequential portion of the code:

$$\lim_{p \to \infty} (S_p) = \lim_{p \to \infty} \left( \frac{p}{\frac{1+p_{T_0}^T}{T_1}} \right) = \frac{T_1}{T_o}$$

Using our earlier example, with  $T_o = T_s/10 - 10\%$  sequential part – the upper bound on the speedup is 10.

If we look at the limit of the speedup using the general overhead function  $T_o(p, n)$ , the result depends on the order of p in  $T_o$

$$\lim_{p \to \infty} \left( \frac{T_1 p}{T_1 + p T_o(p, n)} \right) = \begin{cases} 0 & \text{if } a < 0\\ T_1 / T_o & \text{if } a = 0\\ p & \text{if } a > 0 \end{cases}$$

Where *a* is the order of *p* in  $T_o(p, n)$  as  $p^a$ .

The actual speedup function is more informative than the limit, since in practice we run the programs on computers with a limited number of processors. We are much more interested in the shape of the overhead function and the constants that will determine the final time and speedup curves.

Figure 3-23 and Figure 3-24 illustrate the parallel execution time and speedup curves obtained for a parallel program using different problem sizes and an overhead function with complexity O(p); a = 1 in  $T_o(p, n)$ ,. We can see that for smallest problem size, the overhead quickly becomes the dominating factor and execution time starts increasing again.

Beware! In this case, adding more than 16 processors to the system will slow down our problem; using more than 128 processors will result in longer execution time than the sequential one!

As the problem size is increased, the effect of the overhead becomes smaller and smaller and the performance tends to the ideal. These effects are even more pronounced on the speedup curves. For the smallest problem size the largest speedup is at p = 8, then the system starts to slow down. Increasing the problem size pushes the speedup maximum to larger processor number, p = 32, then it also starts to decline. The largest problem size produces near ideal performance up to 32 processors then it starts to saturate but the speedup still increases. The shape of the overhead function did not change; the ratio of the overhead to the useful computation has a dramatic effect on performance. The art of parallel computing is to optimise a system to minimise overheads by carefully matching the parallel architecture, the algorithm, the programming language and the implementation.

Figure 3-23 Parallel execution time for different problems sizes at linear overhead function.

Figure 3-24 Speedup curves for different problems sizes at linear overhead function.

#### 3.6 CREATING AND EXECUTING PARALLEL PROGRAMS

The process of creating a parallel program is very similar to what we normally follow in designing and implementing a traditional sequential program. The main difference is that the programs are more complex and we really need to pay attention to execution speed and performance.

Once a parallelisation strategy is found for the problem we select a parallel programming language that is suitable for describing our solution and can create executable code for our target parallel computer. For desktop computer use, this is normally not a problem, every language can create code for them (although some compilers/runtimes are not well supported on Windows platforms).

The next step is to design whether or not to use external libraries. Much programming effort can be spared if libraries providing reliable and high-performance algorithm implementations can be used in our program and we do not have to develop the entire code from scratch. Linear algebra libraries are good examples for this. However, in some cases, learning a library can be an equally difficult task. Also, there are third-party libraries that provide mediocre performance. For very specialised problems, using libraries is normally not an option.

While most programs can be developed using a simple code editor and command line compiler commands, large production systems are typically developed in Integrated

Development Environment (IDE). If this is a requirement, one must take into IDE support into consideration too. There are a number of development environments in use, probably the most popular ones at the moment are Eclipse and Microsoft Visual Studio. Eclipse supports parallel development via the Parallel Tools Platform plugin.

The most difficult task in a parallel program development is debugging. Our processes might execute on different machines, there might be temporal and non-deterministic errors. These are very difficult to spot and localise in a parallel program. This is the area where modern development environments are indispensable. It must be noted that parallel numerical programs require extra care when developed. The validity and accuracy of the numerical results must be carefully validated to reference sequential programs in order to guarantee that our program computes correct results at high speed – there is not much use in generating results that are useless but very fast!

The final step of the development process is the performance evaluation step. Once the results are validated, the program should be analysed for execution performance. Performance critical parts of the program should be identified and, if possible, optimised to improve performance even further. Performance optimisation is almost an art. It requires deep knowledge of the algorithm, the execution mechanism and the characteristics of the parallel architecture. It is a combination of various software and hardware parameters that will determine the final performance of the program, therefore this task is very frequently a balancing act requiring many experiments. The built-in parallel profilers in state-of-the-art development environments are invaluable tools in this step, indeed.

Programs running in a global address space computer are relatively straightforward to execute. Normally we set the number of processors to be used in the program then run it. Distributed memory systems are more complicated. We need to configure the system, decide how many processors/computers we would like to use in the system and often manually describe how the processes or our program will be mapped to physical processor cores. There are also systems, however, where operating systems take care of the mapping and execution scheduling of processes, so we can draw the conclusion that the variety of options in parallel program execution are much larger than in the sequential programming world.

# References

- [1] "The History of Computing Project: Cray-1 computer." [Online]. Available: http://www.thocp.net/hardware/cray\_1.htm.

- [2] Wikipedia, "Photograph of the Cray-1 supercomputer." [Online]. Available: http://en.wikipedia.org/wiki/File:Cray-1-deutsches-museum.jpg.

- [3]A. R. Larzelere, "Delivering Insight The History of the Accelerated Strategic Computing<br/>Initiative (ASCI)," 2009. [Online]. Available:<br/>https://asc.llnl.gov/asc\_history/Delivering\_Insight\_ASCI.pdf.

- [4] "Page 2 Intel's 50-core champion: In-depth on Xeon Phi | ExtremeTech." [Online]. Available: http://www.extremetech.com/extreme/133541-intels-64-core-championin-depth-on-xeon-phi/2.

- [5] "High Performance Computing for Servers | Tesla GPUs | NVIDIA." [Online]. Available: http://www.nvidia.com/object/tesla-servers.html.

- [6] G. Amdahl, "Validity of the Single Processor Approach to Achieving Large-Scale Computing Capabilities," in *AFIPS Conference Proceedings (30)*, 1967, pp. 483–485.

- [7] J. L. Gustafson, "Reevaluating Amdahl's Law," *Commun. ACM*, vol. 31, pp. 532–533, 1988.

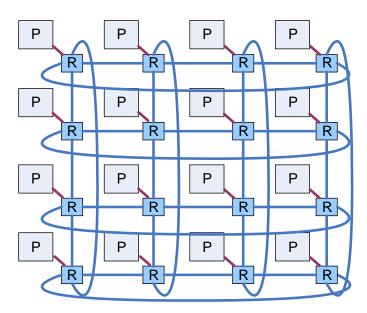

Parallel computing is about using multiple processors to reduce program execution time. The processors we intend to use during our computation must form a computing device that is capable of executing parallel programs. In this part of the book, we explore various ways of building multiprocessor computers. We will discuss the architectural, engineering and often economic constraints that influence the type of parallel computer we can create. We will also look at the history of architecture development, which is very important as many ideas that once looked impractical may – and do – reborn later when we encounter a technological paradigm shift. Since the field of parallel computer architecture is vast, we will only cover the most important aspects in this part in order to introduce the reader to the most fundamental issues.

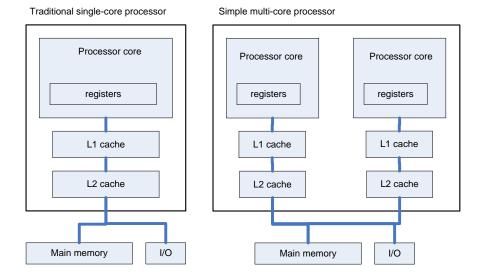

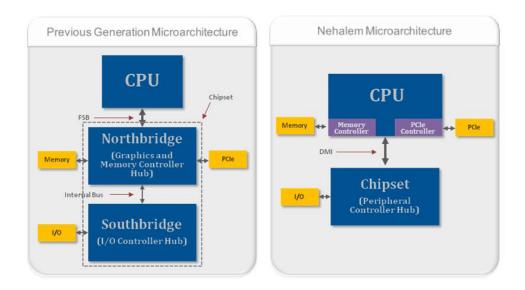

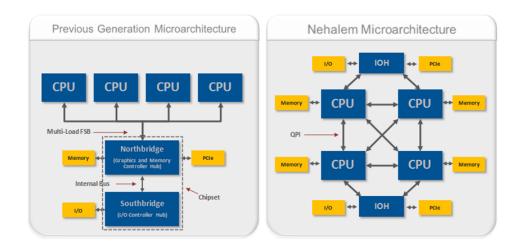

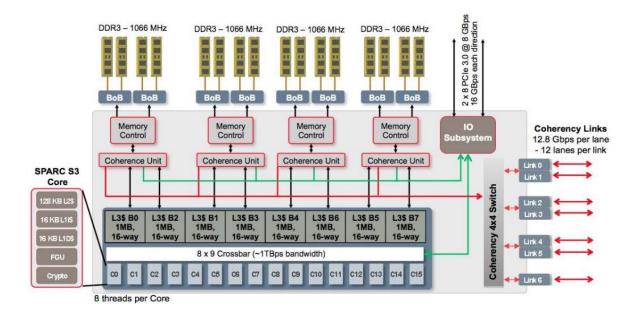

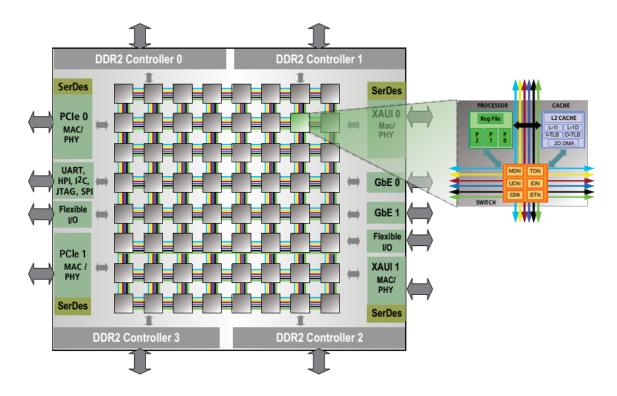

Let us first look at what we need to build a parallel computer. We certainly need processors, memory and some sort of interconnection device that will connect the various parts of the system (typically processors and memory). These are the basic building blocks (components) of any parallel system. Based on the way we interconnect these components we can create two fundamentally different types of parallel computing systems: *shared-memory* and *distributed memory* parallel architectures. Shared-memory systems are often called tightly-coupled systems, whereas the ones using a distributed memory architecture are called loosely-coupled systems. As we will see when we discuss the programming aspects, in tightly-coupled systems, processes communicate via shared variables; in loosely-coupled systems communication is achieved by message passing.

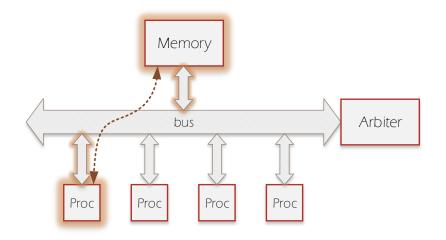

## 4.1 SHARED-MEMORY COMPUTERS

An archetypical shared-memory multicomputer, as shown in Figure 4-1, consists of a set of processors and one global memory module. The processors are connected to the memory via a common, shared system bus. The system bus in our discussion will always include the address, data and control buses. Each processor accesses the same memory module and each of them reads from and writes to the same address space. This architecture is the obvious extension of the von Neumann type architecture, in which the processor is connected to the memory via a bus. It is not surprising that the first parallel computers are extensions of this very well understood sequential architecture.

#### 4.1.1 The operating mechanism of a single-bus shared-memory multicomputer

When we use multiple processors in a bus-based system, we cannot let processors use the bus at their will. Since the bus can accommodate data transfer for only one processor at any one time, access to the bus should be controlled. Normally, a bus *arbiter* is used for this purpose. Whenever a processor wants to access the memory, it must request the use of the bus from the arbiter by sending it a *request signal*. Based on the request, if the bus is not busy, the arbiter *grants* the right of using the bus to the requesting processor and the memory operation can begin. While the processor-memory data transfer is in place, the bus becomes blocked for other processors; any other processor wishing to use the bus will have to wait. Once the memory operation is complete, the processor releases the bus, and consequently the other arbiter can grant access to the bus for the other processors.

Figure 4-1 The architecture of a typical shared-memory system. Processors access memory via the shared bus.

#### Bus arbitration methods

There are various common rules based on which the arbiter can decide which processor's bus request to grant when multiple competing requests are received. The most common such methods (arbitration policies) are the following ones [8].

**Static daisy chaining** — This is a static policy in which priority is attached to system components based on their location on the system bus relative to the bus control unit. The closest component has the highest priority. This scheme is not used frequently in parallel computers; it is more common in industrial systems where additional processors are used to control peripheral devices or provide backup in failure situations.

**Fixed time slice** (round robin) — In this scheme, fixed-length time slices are allocated to each processor during which it is allowed to use the bus before the next component takes over. The method is executed in a cyclic manner giving a chance for each processor in turns. Each component has equal priority and the service does not depend on the location of the component. This method provides good load balancing but waiting times can be high if the number of processors is too high. This policy is the most commonly used in parallel computers.

**Least served first** — Under this dynamic scheme, the highest priority is given to the processor that has not used the bus for the longest time. After each bus access operation, a new priority is calculated. This method provides good load balancing with shorter waiting time than the static round robin one. (Interestingly, this kind of priority boost is frequently used by operating systems for giving a chance for low-activity processes in order to avoid starvation.)

**First-come, first-served** — In this arbitration policy the bus is granted to processors in the order of their requests. The processor placing the request first will receive the bus first. This method is not easy to implement – queues are necessary – but provides the best average waiting times among all schemes. Its drawback is that bad load balance may introduce scheduling problems; high-activity processors will dominate bus usage.

The main attraction of bus-based shared-memory architecture is its simplicity. Since it is the straightforward extension of the type of computer architecture the industry has been using for the past fifty years, the technology is very mature. Creating parallel systems based on the modification of the original sequential architecture hence is relatively simple.

There is, however, one crucial problem with this type of architecture and that is the shared bus. Since processors have to share the bus and only one can use it at a time, all processors except one will always have to wait for the bus. This is what we call *resource contention*. Why is the shared bus a major problem? If we increase the number of processors in the system, processors will have to wait more and more for the bus. For a small number of processors we can, in theory, increase the speed of the bus so it could service more processors within the same amount of time, but the speed of the bus obviously cannot be increased without limits. Consequently, as we add more and more processors to our system, the bus will become more and more busy – in other words the bus becomes *saturated* – and the processors eventually will spend more time waiting than working. The

performance of the system will halt, i.e., after a certain threshold, adding more processors will not increase the computing power of the computer.

With this approach, only a very limited number of processors can be used effectively. If we would like to achieve, say, teraflops performance, which requires thousands of today's processors to be used collectively, this is not a viable architecture. In the following sections we explore ways that can improve the performance of bus-based architectures [8].

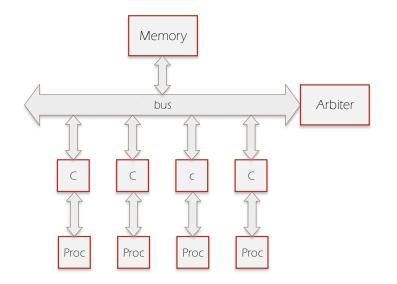

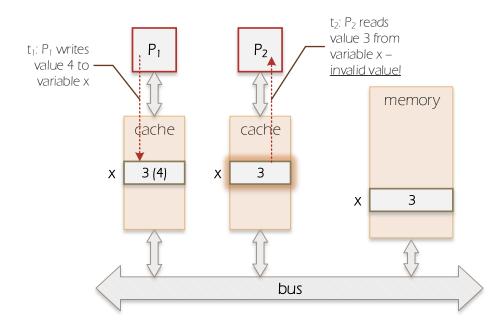

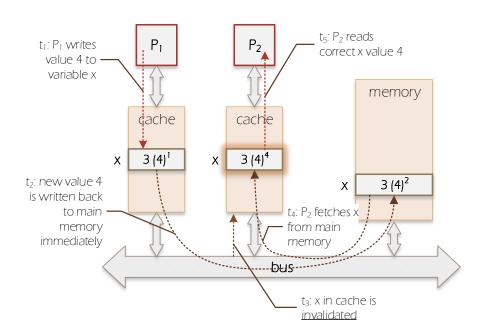

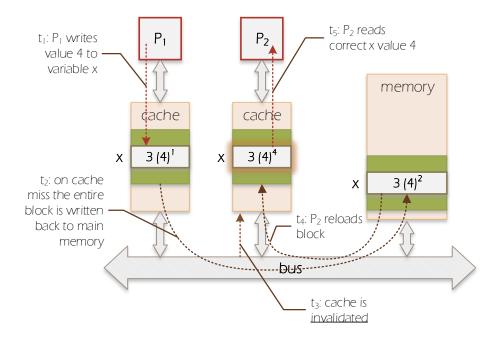

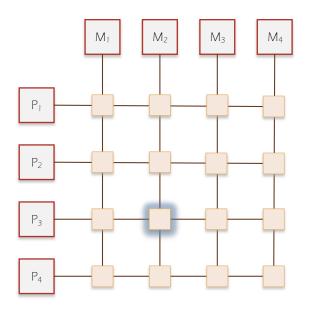

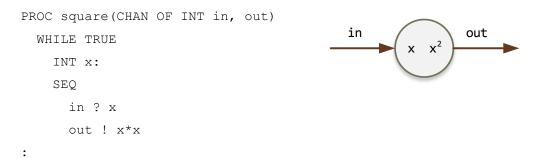

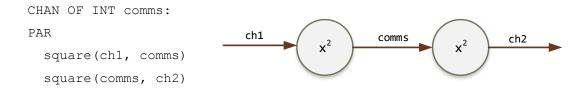

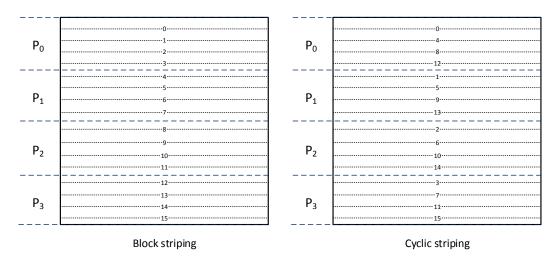

#### 4.1.2 The cache-based shared-memory multicomputer